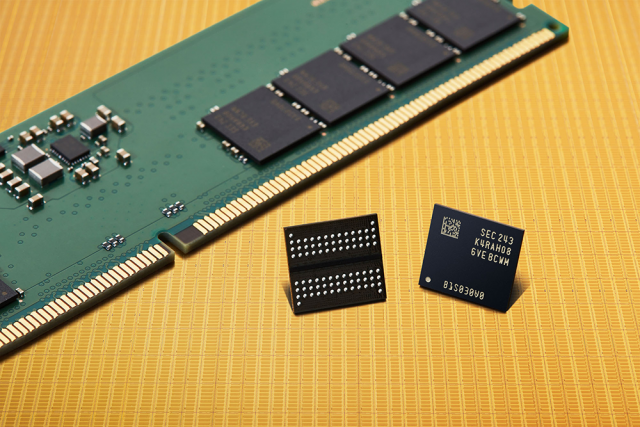

독자 여러분, 안녕하세요. 지난 21일 삼성전자(005930)에서 새로운 D램 반도체를 출시했죠. 일명 12나노급 16Gb DDR5 EUV D램. 처음 보신 분들은 나열된 용어들이 마치 암호처럼 느껴지실 수도 있을 것 같은데요.

그래서 준비했습니다. 간단하게 삼성전자에서 설명한 보도자료 원문의 키워드를 가져와서 이 D램이 어떤 반도체인지, 어떤 의미를 지니고 있는지 살펴보려고 합니다. 총 7가지 재밌는 이야기를 발견할 수 있었습니다. 총 두편으로 나뉩니다. 1편에서는 총 3가지 이야기를 다룹니다. 2편에서는 나머지 4개 스토리를 담고 있습니다.

1. 삼성전자, 업계 최선단 12나노급 D램 개발

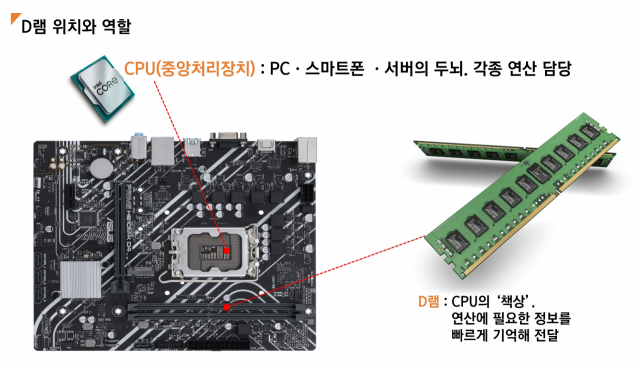

D램이 무슨 장치인지부터 짚고 넘어가봅시다. D램은 골프로 따지면 '캐디'와 비슷한 역할입니다. 골퍼가 탁 트인 골프장에서 스윙을 한다고 가정해볼까요. 캐디는 바로 옆에서 가방을 들고 다니면서 상황에 따라 필요한 골프채를 건네죠. 풍향, 현재 위치 등을 꼼꼼하게 기록해뒀다가 스윙 직전에 귀띔을 해주기도 합니다. D램은 캐디 같습니다. 중앙처리장치(CPU)가 전자기기가 필요한 각종 데이터 연산에 집중한다면요. D램은 CPU 바로 옆에서 연산에 필요한 정보를 기억했다가 빠른 속도로 전달하는 장치입니다. 사실 이 역할을 하는 1차 메모리는 'S램'이 있습니다. 그러나 S램은 용량이 아주 작아서 정말 급한 용무만 해결하고요. 대부분 정보 저장과 CPU와의 정보 공유는 용량이 큰 D램이 합니다. '주 기억장치'라고 불리는 이유죠.

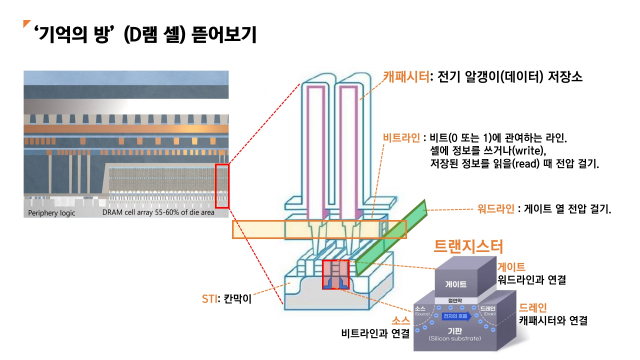

그럼 D램 바로 앞 수식어인 '12나노급'은 무엇일까. 먼저 D램 속을 좀 자세히 들여다봐야 합니다. 먼저 전기 알갱이, 즉 전자를 저장하는 기다란 통 모양 '커패시터'가 가장 눈에 띕니다. 저장소 속에 전자들이 꽉꽉 채워지거나 빠지면서 '0' 또는 '1'이라는 디지털 신호를 기억하는 곳입니다. 커패시터 앞에는요. 전하들이 저장소로 도달하거나 그렇지 못하도록 교통정리를 하는 녀석이 있습니다. 이 친구를 '트랜지스터'라고 합니다. 지금부터 트랜지스터와 커패시터를 합쳐서 '기억의 공간'이라고 부르겠습니다. 전문 용어로는 'D램 셀(Cell)'입니다.

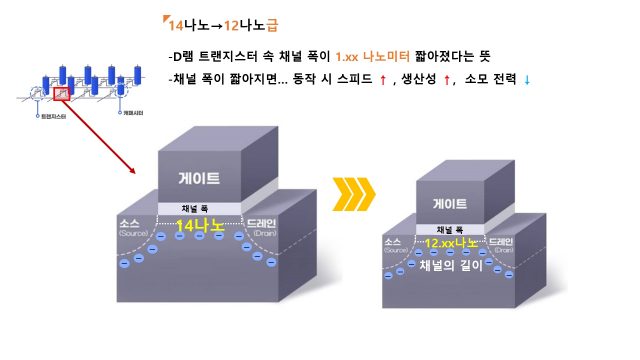

12나노급이라는 표현은 말이죠. '트랜지스터' 안에서 전자가 이동하는 통로(채널) 폭이 12.몇 나노미터(㎚·10억분의 1m) 정도 된단 얘기입니다. 이 길이는 갈수록 짧아지고 있습니다. 12나노급 D램 개발 직전인 2021년 10월 삼성전자가 14나노 D램을 개발했다고 발표했죠. 최신작인 12나노급 D램은 전 세대보다 채널의 길이를 약 1.몇 nm 더 작게 만들었다는 걸로 풀이할 수 있습니다.

2. 12나노급 16기가비트(Gb) D램은 이전 세대 제품 대비 생산성이 약 20% 향상됐다.

아니 그러면, 이 채널의 길이는 왜 점점 줄이려는 걸까. 다양한 원인이 있는데요. 가장 큰 이유는 생산성과 직결되는 문제이기 때문입니다. 트랜지스터 채널의 길이, 즉 선폭을 줄일수록 이익을 더 많이 남길 수 있다는 이야기죠. 조금 더 자세히 이야기해 봅시다. D램 안에 있는 기억의 공간은 한 두개만 있는 게 아닙니다. 이번 보도자료에서 언급된 16Gb가 바로 '기억의 공간' 개수를 나타내는데요.

Gb에서 비트(b)는 0또는 1을 의미합니다. 기가(G)는 2의 30승, 약 10억을 뜻하고요. 그러니까 16Gb는 160억 여개의 0 또는 1을 저장하는 '기억의 공간'이 한 칩 속에 들어가있단 걸 뜻합니다.

자, 14나노에서 12나노급으로 줄어들었다는 건 이 160억개 기억 공간의 게이트 길이가 일제히 줄어들었다는 걸 뜻합니다. 그럼 어떤 일이 벌어질까요. 같은 스펙으로 기억 공간을 160억개 만들더라도 폭이 줄었으니 더 몸집이 작은 D램 칩이 나오게 됩니다.

이젠 나무가 아닌 숲을 봅시다. 반도체는 동그란 웨이퍼 위에 만들어집니다. D램 칩이 확 작아지면 한 개 웨이퍼에 생산할 수 있는 D램 수가 더 많아진다는 얘기이기도 합니다.

그럼 한 웨이퍼 위에 더 많은 D램을 만들 수 있는 거니까 물량이 훨씬 늘어나고, 양이 늘어났으니 D램 가격을 다른 곳보다 낮출 수 있겠네요. 한마디로 더 싸고 좋게 만들 수 있다는 겁니다.

삼성전자는 이번 기술 개발로 D램 생산성을 20% 올렸다고 밝혔습니다. 생산성 향상의 기준을 정확히 확인할 수는 없습니다. 허나 만약 이 기준을 칩 개수로 가정한다면 한 개 웨이퍼에서 1000개 만들 걸 1200개로 늘렸다는 '추측'을 할 수 있겠습니다. 또 만약 동일하게 1000개를 만든다고 해도 동일 면적에 트랜지스터가 더 많이 들어간, 용량 큰 메모리를 만들 수 있단 의미이기도 하겠네요. 기술의 발전입니다. 어느 쪽이든 웨이퍼 한 장이 갖는 부가가치는 커지는 셈입니다.

채널 폭을 줄이는 이유는 생산성 외에도 다양합니다. 우선 D램 속도가 빨라집니다. 이걸 우리 사는 세상에 비유하면요. 마치 출퇴근·등하교길이 짧아지는 것과 같습니다. 같은 속도라도 거리가 짧아지면 데이터가 훨씬 빨리 이동할 수 있겠죠? 세상은 범람하는 데이터를 빨리 처리하기 위해 속도감 죽이는 D램을 원합니다. 따라서 채널 길이를 줄면서 D램 속도를 높여나가는 게 D램 회사들의 미션입니다.

3. 이 제품은 이전 세대 제품보다 소비 전력이 약 23% 개선됐다

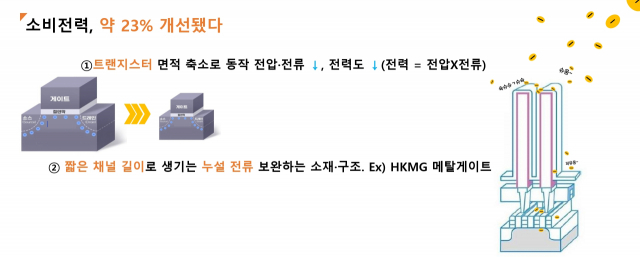

게이트 길이를 줄이면 에너지 효율에도 긍정적인 영향을 줍니다. '기억의 공간'에는 이들이 열심히 정보를 쓰고 지우고, 유지하는 일을 할 수 있도록 '전압'을 제공해줘야 합니다. 이때 필요한 전력들이 트랜지스터와 큰 연관이 있습니다. 트랜지스터 선폭이 짧아지면 말이죠. 동작 전압과 전류가 낮아져서 전력 효율 향상으로 이어집니다.

반대로 D램이 열심히 일하지 않고 저장된 전자들을 가두고만 있을 때도 전력 소모가 있습니다. 전자들이 새어나가면서 원치 않는 전류의 흐름이 발생하기 때문인데요. 문제는 게이트의 선폭이 줄어들수록 그런 전력 소모가 많아진단 겁니다. 아무래도 게이트가 좁아지면 탈출구까지 거리가 짧아지는 셈이니 질풍노도의 전기 알갱이들이 더 잘 도망다니는 것이죠. 트랜지스터 채널 길이가 짧아지면서 발생하는 비이상적 현상, 이른바 숏 채널 효과가 핵심 키워드입니다. 이 문제가 심화하면서 학계와 산업계에서는 원치 않는 전력 소모를 줄일 새로운 방안을 찾고 있습니다.

종합해보면 이번에 삼성이 소비전력을 23% 개선했다는 건 △'기억의 공간' 채널 단축과 면적 축소로 동작에 활용되는 전압이 낮아지고 △누설 전류를 줄일 수 있는 다양한 소재·설계 기술을 복합적으로 결합해 에너지 효율을 도모했을 가능성이 큽니다.

스마트폰에서든 데이터센터에서든 사용자가 동일 용량의 D램을 사용했을 때 전력 소모가 감소되는 것은 꽤 의미있는 일입니다.

다만 한가지 더. 사실 전력 효율 이야기가 나온 김에 전력 소모에 대한 거시적인(?) 고민도 한번 짚어봐야 합니다. 한 개 D램 '기억의 공간' 전력이 20% 이상 줄었다고 해도 말이죠. 전체 ‘웨이퍼’ 수준에서도 전력 소모가 이만큼 줄었는지 한번 냉정하게 생각해볼 필요도 있습니다.

이건 또 무슨 이야기냐고요. 2번에서 이야기한 “동일한 1000개를 만들더라도 더 많은 트랜지스터를 집어 넣을 수 있다”는 설명과 관련 있습니다.

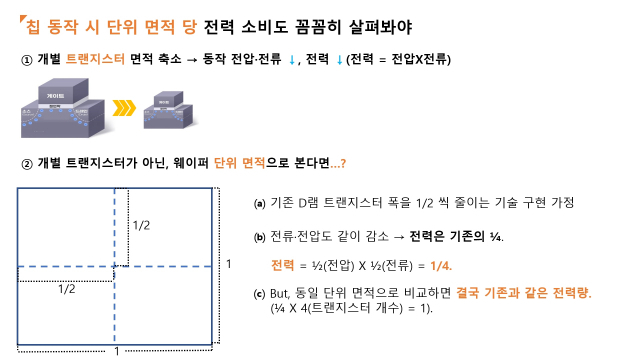

위 그림과 함께 극단적 예를 봅시다. 어떤 12인치 웨이퍼에 단 1개 트랜지스터를 만들 수 있다고 봅시다. 이 트랜지스터의 가로, 세로 폭을 절반으로 줄이는 획기적인 공정 기술이 개발됐다고 가정할게요. 그럼 같은 면적에 4개의 트랜지스터를 집어넣을 수 있게 되겠죠?

반도체 소자 설계 룰에 따르면요. 트랜지스터 크기가 줄면 전류와 전압도 그만큼 줄어듭니다. '전력=전류 X 전압' 공식을 적용하면 1/2 x 1/2니까 한 '기억의 공간' 전력은 기존보다 4분의 1로 줄어듭니다. 이까지는 좋죠?

그런데 문제는 이 광경을 더 높이서 봤을 때 보입니다. 우리는 아까 1개 트랜지스터를 만들 자리에 결과적으로 4개 트랜지스터를 집어넣을 수 있게 됐다고 했는데요. 그럼 각각 트랜지스터의 전력 합해볼까요? 1/4 X 4라서 결국 1. 12인치 웨이퍼 전체에 심어진 새로운 트랜지스터들의 전력 합은 기존 1개 커다란 트랜지스터 전력량과 같다는 결론에 이르게 됩니다. 웨이퍼가 아닌 칩 단위로 잘라서 보더라도 마찬가지 이야기가 됩니다. 만약 기술 고도화로 8Gb(8억개 셀) 칩 면적에 전력 개선을 한 트랜지스터16Gb(160억 개 셀)를 심었다고 해도, 전체 전력은 기존과 큰 차이가 없을 것이라는 결론이죠.

물론 D램 안에는 트랜지스터 외 다른 요소와 변수가 너무 많아서 트랜지스터 축소만으로 전력 효율성을 따지긴 힘듭니다. 다만 트랜지스터 동작 전력이 D램에서 꽤 중요한 부분을 차지한다는 점에서 그냥 넘어갈 문제도 아닙니다.

다만 면적 축소와 함께 전력 효율성을 획기적으로 올릴 수 있는 방안이 마련돼야 한다는 의견이 나옵니다. D램 전문가 조성재 가천대 교수는 "동작전압을 낮추고 원치않는 누설 전류를 최소화하는 것이 가장 큰 과제"라며 "특히 정보 유지 시간을 늘리고 비동작시 전력 소모를 낮추려면 누설 전류를 막는 일이 상당히 중요한데, 신뢰성 있는 소재와 독특한 구조 관련 원천 기술을 개발하는 것이 핵심"이라고 설명했습니다.

2편으로 넘어갑니다. 2편에서는 D램의 속도, DDR5와 EUV, 커패시터에 관한 이야기가 나옵니다.