삼성전자 파운드리(반도체 위탁 생산) 사업부가 차세대 기술인 후면전력공급(BSPDN) 장치에 대한 자신감을 다시 한 번 드러냈다. 칩 크기 축소로 전력효율과 성능을 모두 잡을 수 있을 것으로 내다봤다.

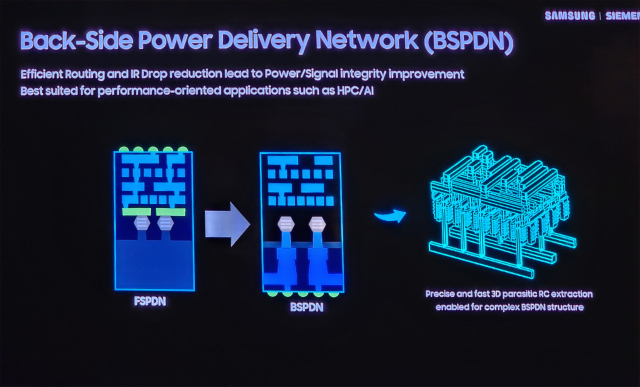

이성재 삼성전자 파운드리사업부 상무는 22일 서울 송파구 롯데호텔에서 열린 ‘지멘스 EDA 포럼 2024’ 기조연설자로 나서 이같이 밝혔다. 이 상무는 “BSPDN 기술은 전면전력공급 장치보다 반도체의 면적을 17% 줄일 수 있고 전력효율과 성능을 각각 15%, 8%씩 올릴 수 있다”고 말했다. 삼성 파운드리가 대외적으로 자사 BSPDN 성능을 언급한 적은 처음이다.

BSPDN 기술은 삼성전자가 2027년부터 2㎚(나노미터·10억분의 1m) 파운드리 공정부터 도입할 기술이다. BSPDN은 연산 장치에 공급하는 전력 배선을 반도체 뒷면에 배치하는 기술이다. 회로와 전력 공급 영역을 분리하면서 칩의 성능을 극대화할 수 있지만 공정이 상당히 까다롭고 난도가 높다. 인텔·TSMC 등 삼성전자의 라이벌 회사들도 상용화에 도전하고 있어 미래 파운드리 시장에서 상당히 중요한 기술로 주목받는다.

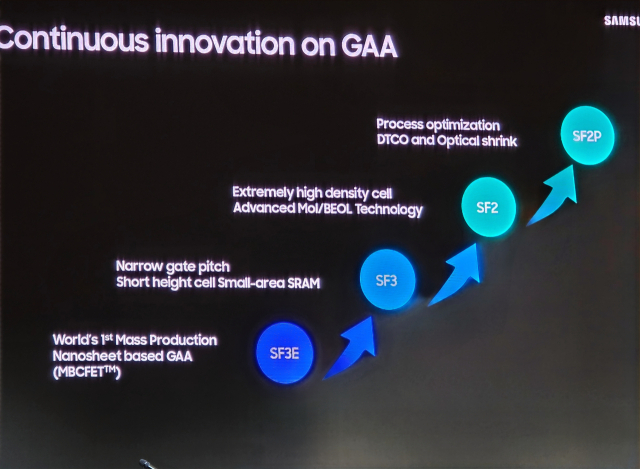

이 상무는 이어 삼성전자의 차세대 게이트올어라운드(GAA) 회로 성능에 대해서도 발표했다. GAA는 삼성전자가 2022년 세계에서 처음으로 반도체 공정에 도입한 소자 구조다. 이 상무는 “올해 양산 준비 중인 2세대 GAA(SF3)의 성능과 전력효율은 각각 30%, 50%씩 개선됐고 면적은 35% 감소했다”고 밝혔다.

그는 삼성전자가 2026년 파운드리 공정에 적용할 4세대 GAA(SF2P)의 경우 3세대 GAA(SF2)보다 전력효율이 25%나 좋아지고 연산 성능은 12% 개선되면서 칩의 면적은 8% 감소할 것으로 기대했다.