TSMC. 요즘 한국 반도체 기사에서 가장 많이 등장하는 외국 칩 제조사가 아닐까 싶은데요. 50% 이상 점유율로 세계 파운드리 1위. 삼성전자의 3나노 라이벌. 대만의 강력한 실리콘 실드. 반도체 위탁생산(파운드리) 분야에서 독보적인 영향력을 과시하고 있습니다.

그런데 독자 여러분, 파운드리 현재 폼 원탑인 TSMC는 미래를 어떻게 준비하고 있는지 궁금하신 적 없나요? 3나노(㎚·10억분의 1m), 2나노 등 단기적인 로드맵 외에도, 수년 뒤에 구현할 반도체 구조·소재에 대해서요.

그래서 준비했습니다. 오늘은 지난 6월 'VLSI 2022'라는 세계 최대 반도체 학회에서 TSMC R&D부문 주요 임원 미위졔(米玉傑) 수석부사장이 발표한 내용을 뜯어보고, TSMC의 미래 로드맵을 한번 짚어봤습니다. 패키징에 관한 이야기까지 총 2편으로 나뉩니다. 지금 나온 기술들은 TSMC 뿐만 아니라 미래 반도체 시장 전반에서 화두가 될 이슈이기도 한 것 같습니다.그럼 우선 신박한 반도체 구조인 'CFET'부터 살펴봅시다.

◇3D 반도체를 쌓은 CFET

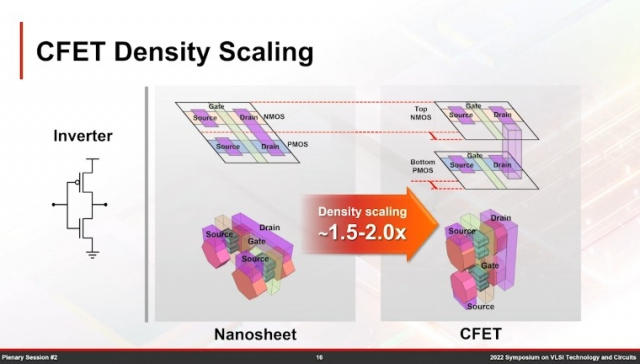

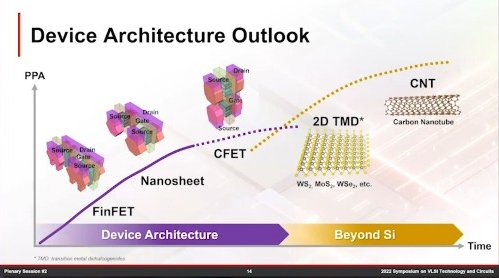

TSMC 발표 슬라이드를 관통하는 키워드는 트랜지스터 '면적 줄이기(scaling)'입니다. 반도체 속 연산 장치인 트랜지스터 크기를 어떻게 하면 더 작게 만들어서 같은 공간에 최대한 많이 욱여넣을 수 있을까 궁리한 거죠. 먼저 이들이 구현하고자 하는 'CFET'이라는 컨셉부터 보시죠.

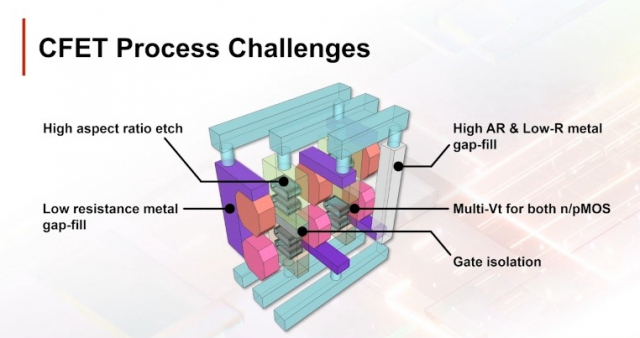

그림을 보면 조립형 장난감 블록을 복잡하게 쌓아놓은 것 같죠? 하나하나 풀어봅시다. CFET은요. 집적도 향상을 위해 2차원(2D)의 트랜지스터 배치 구조를 3D, 적층으로 바꾼 것이 핵심입니다.

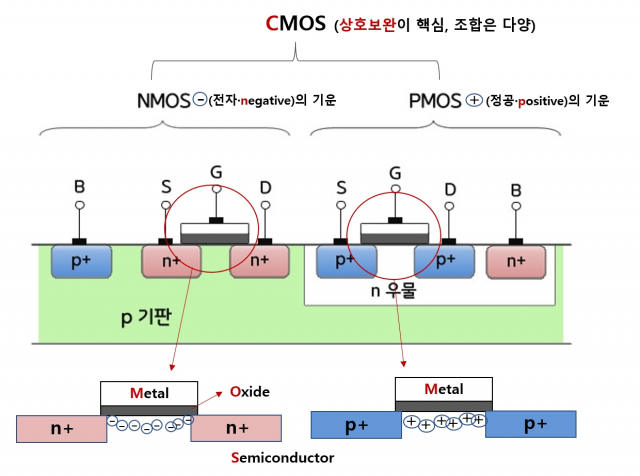

먼저 이 구조를 이해하려면 우리는 CMOS 개념을 짚고 넘어가야 합니다. CMOS는 한마디로 n반도체 스위치(nMOS)와 p반도체 스위치(pMOS)가 힘을 합쳐 연산하는 트랜지스터입니다. 더 파고 들어가볼까요?

CMOS에서는 알파벳 'C'를 유심히 보셔야 하는데요. C는 '상호보완적'이라는 뜻의 'Complementary'를 줄인 말입니다. 무엇이 상호보완적이라는 것일까. 반도체 소자 종류는 크게 nMOS와 pMOS가 있습니다. 상황에 따라 스위치를 켜거나 끄면서 전기 신호를 흘리거나 막는 역할을 합니다.

nMOS와 pMOS는 상극입니다. nMOS는 (-) 전기 알갱이(전자)가, 반대로 pMOS는 (+) 전기 알갱이(정공)가 전류를 나르기 때문인데요.

그런데 이 둘을 붙여 놓으면 의외로 궁합이 좋습니다. 마치 세계적인 K-팝 가수 지드래곤과 태양이 서로 특기가 달라도 합치면 최상의 퍼포먼스를 뽐내는 것처럼 말이죠. 그래서 '상호보완(C)'이라는 용어가 붙습니다.

CMOS 반도체의 대표적 예는 '인버터'입니다. 중앙처리장치(CPU) 등 주로 '두뇌'역할을 하는 칩에서 연산 장치에 활용되는 소자 구조입니다.

인버터는 nMOS, pMOS가 한 개씩 나란히 결합한 소자입니다. 0을 넣으면 pMOS가 켜지면서 1을, 반대로 1을 넣으면 nMOS만 동작하며 0을 출력해내는 등 결과 값을 뒤집어서(invert) 내놓는 소자죠. 이렇게 하면 단일(n또는 p) 소자로 만들 때보다 전력 효율이 훨씬 좋습니다. 소자가 동작할 때 n, p 중 하나는 반드시 꺼지는 원리라, 스위치 켜는 것 외에는 딱히 전력 들 곳이 없거든요.

이런 CMOS도 문제가 있습니다. 바로 '면적'입니다. n,p 중 한 개만 놓으면 될 자리에 두 개 소자가 나란히 놓이는 셈이 됩니다.

이 문제는 3나노 공정 이하 시대로 접어들면서 더 큰 고민 거리가 됩니다. 만약 n,p MOS의 크기를 줄일 수 없는 지경까지 다다른다면 무슨 방법을 선택해야 할까.

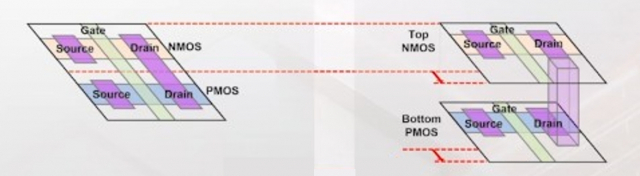

이 물음에 답하기 위해 TSMC가 꺼내든 카드는 'CFET'입니다. 나란히 자리한 두 소자를 종이접기 하듯 반으로 접어서 세로로 쌓는다는 거죠.

쌓는다는 개념. 반도체 기사 보시면서 많이 들어보신 단어죠. 맞습니다. 3D 낸드플래시에서 저장 공간을 수평에서 수직으로 세워 쌓아 올리는 방식을 택한 것처럼, CPU 속 '인버터'라는 장치도 궁극적으로 쌓아올리겠다는 포부를 밝힌 것입니다.

수평으로 놓여있던 걸 세로로 세워 쌓아올렸으니까 기존보다 공간 효율이 좋겠죠. 따라서 인버터 수를 1.5배~2배 정도 더 늘릴 수 있다는 설명도 덧붙이네요.

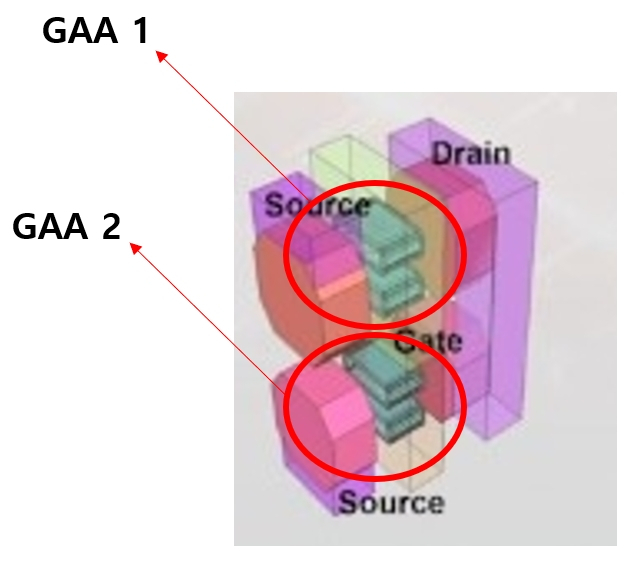

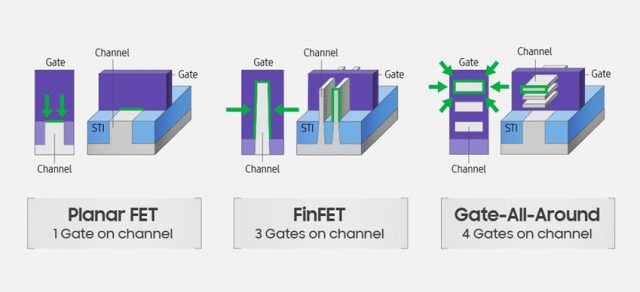

여기서 잠깐. 삼성전자가 얼마 전 발표한 게이트올어라운드(GAA) 개념과는 어떻게 다른 건지 궁금해하실 분도 있으실텐데요. GAA는 n 또는 p 반도체, 그러니까 개별 소자를 만들 때 활용되는 구조입니다. GAA는 전압을 거는 게이트와 전류가 흐르는 통로인 채널이 닿는 면을 늘려서 데이터 처리 속도를 늘린다는 콘셉트인데요. 삼성전자는 이번 3나노 공정에서 반도체 인버터의 n반도체에 GAA를 적용한 것으로 알려져 있습니다.

TSMC CFET의 그림을 아주 자세히 보시면, GAA로 만든 n반도체 위에 비슷한 형태로 만든 p반도체를 쌓은 것을 볼 수 있습니다.

정리를 하면 기술의 발달 순서를 보면 평면→핀펫→GAA(나노시트)→GAA 반도체 여러 개를 쌓는 CFET 까지 진화할 거라는 걸 예상할 수 있겠네요.

CFET은 아직 많은 과제가 있습니다. 우선 p반도체를 n반도체 위로 올려버리면서 생기는 게 도전입니다. 실리콘 웨이퍼 위에 올리던 걸, n반도체 위에 '쌓는' 것 자체가 패러다임 변화죠.

n·p반도체 스위치를 연결하는 각종 배선 모양 변화도 있습니다. 각종 라인이 수평에서 수직 모양으로 바뀌기 때문에, 더 깊게 파야되고 선택적으로 정교하게 막을 올려야 합니다. 과연 TSMC는 어떻게 이 과제들을 풀어낼까요.

또 TSMC 점유율을 바짝 추격하는 파운드리 라이벌 삼성전자가 이 기술을 먼저 선점할 가능성은 얼마나 될까요? 차세대 반도체 구조가 차세대 반도체 최대 관전 포인트가 될 것 같습니다.

◇반도체 안에 연필심(흑연)이 들어간다고?

TSMC의 CFET 발표 다음으로 흥미로웠던 부분이 '소재'에 대한 이야기입니다. 제 나름대로는 '비욘드(beyond) 실리콘'이라는 표현도 썼죠. 실리콘으로 만들었던 부분들을 완전히 새로운 소재들로 바꾼다는 얘기죠.

소재 중에서도 △채널 △소스·드레인 △배선(인터커넥트) 부분으로 세분화해 설명드려볼게요. 우선 채널. 채널은 트랜지스터 속에 전압이 걸리면 전기 알갱이들이 이동할 수 있는 통로입니다.

이 채널에 대한 이야기를 할 때 빠지지 않는 이슈가 바로 '숏 채널 이펙트(short channel effect)'입니다.

3나노, 2나노 공정에서 이 숫자들은 트랜지스터의 폭을 말하죠? 공정 미세화로 트랜지스터 폭이 줄어들수록, 채널 길이와 폭도 영향을 받습니다. 전자가 이동하는 통로 조건이 상당히 열악해진다는 거죠.

우리 운전할 때 8차선 고속 도로에서 1차선 도로로 좁아질 때 가장 큰 차이가 '교통 체증'이잖아요. 게다가 경로를 이탈해 도망나가는 전기 알갱이들도 속출합니다.

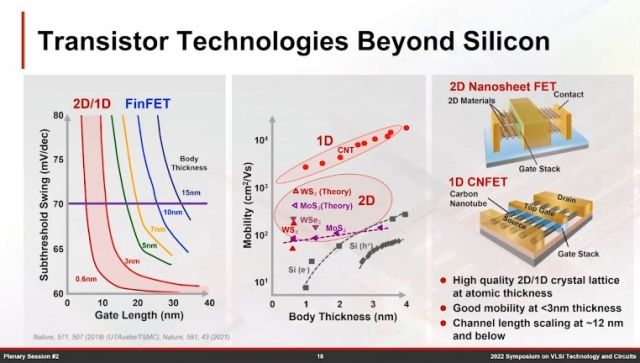

숏 채널 문제를 해결하기 위해 TSMC가 꺼내든 게 바로 소재혁신입니다. '나노시트'와 '탄소나노튜브'. 실리콘이 아닌 완전한 신소재를 쓰겠다는 건데요.

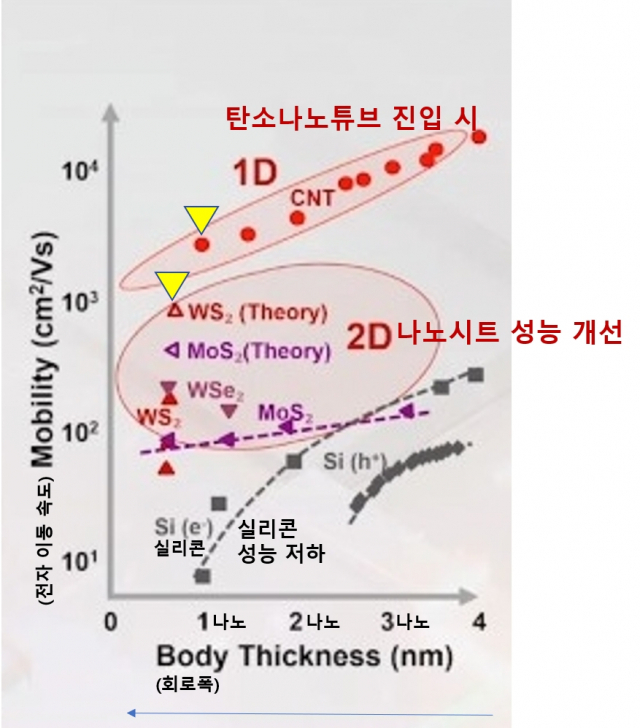

TSMC의 자료에 따르면 채널의 모양이 면(2D) 형태인 GAA 구조에서는 채널 소재를 실리콘에서 이황화텅스텐(WS2), 이황화몰리브덴(MoS2), 이셀레늄화텅스텐(WSe2) 등으로 바꾸는 방법을 연구 중이라고 발표했습니다.

더 미래에는 트랜지스터 폭이 1나노 이하로 줄어드는 것을 대비해 2D(면·나노시트)에서 1D(선)로 바꾸려는 아이디어도 구상 중인데요.

이때 등장하는 게 다양한 산업 분야에서 차세대 소재로 각광받는 탄소나노튜브(CNT) 입니다. 탄소나노튜브 주요 소재는 '흑연'입니다. 우리가 자주 쓰는 연필·샤프심의 주요 구성물이 바로 흑연이죠.

강도가 철보다 100배 가량 뛰어나서 튼튼한데다, 구리와 맞먹는 전기 전도도 성질까지 지니고 있으니 실리콘 대체 소재로는 안성맞춤입니다.

CNT로 만든 채널에 대한 가장 적절한 비유는 일론 머스크 보어링컴퍼니(테슬라) CEO가 최근 공개한 '베이거스 루프'입니다. 미국의 극심한 교통 체증에 짜증이 난 머스크는 아예 지하에 원통형 터널 '루프'를 뚫어 190㎞/h 속도로 차를 운반하겠다는 계획을 실현 중이죠. 반도체 소자에서는 CNT 채널이 루프 역할을 할 걸로 보입니다.

그럼 다시 TSMC가 제시한 그래프를 보실까요. 선폭이 줄어들 수록 실리콘의 전기 알갱이 운반 성능은 확연히 꺾이죠. 반면에 각종 나노시트(2D) 소재, 특히 CNT는 기존 실리콘보다 훨씬 더 좋은 성능을 보이고 있습니다.

다만 CNT의 경우 실리콘에 비해 가격이 상당히 높은데다 원통의 직경과 모양을 제어하는 것이 지금까지는 너무 힘든 것으로 알려집니다. 기술적인 발전이 더 필요할 것으로 보여집니다.

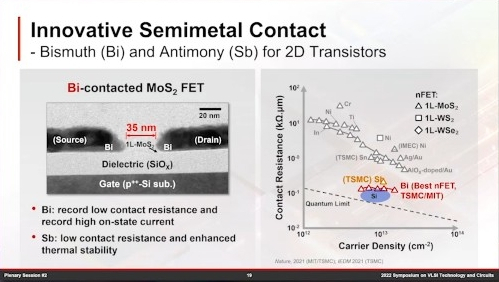

채널 외에도 TSMC는 '소스'와 '드레인' 부분의 소재 개선 내용도 언급합니다. 트랜지스터 내 전기 알갱이를 흘려주는 소스, 알갱이가 바깥으로 배출되는 드레인을 실리콘이 아닌 다른 물질로 대체할 수 있다는 것인데요.

알갱이가 흐를 때 실리콘보다 저항이 낮은 비스무트(Bi), 낮은 저항을 가지면서 고온에도 잘 견디는 안티몬(Sb)같은 소재를 통해 소스와 드레인을 만들 수 있다고 소개했습니다.

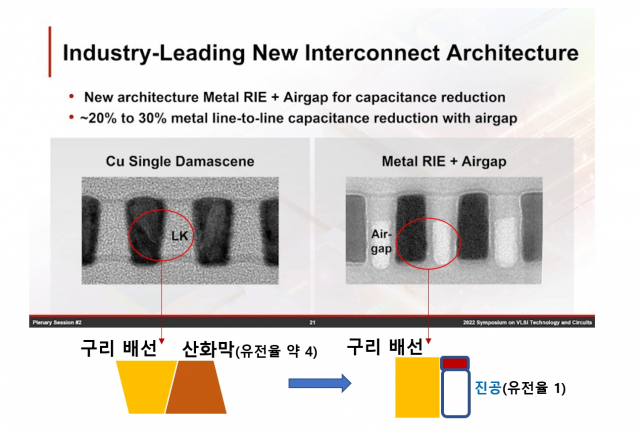

아울러 반도체 트랜지스터를 내·외부와 연결하는 칩 상단의 구리 배선(인터커넥트)부분 공정 개선에 대해서도 언급했습니다.

TSMC는 구리 배선 모양을 아주 정갈하고 수직적으로 깎아내고, 배선의 틈을 기존 산화막(SiO2)으로 메우지 않고 '진공(에어갭)'상태로 만들 수 있다는 걸 현미경 사진으로 공개했습니다.

산화막(녹이 슨 막)은 전기 알갱이를 잡아당기는 힘인 유전율이 '3.9~4.2' 수준이라면, 진공은 4분의 1 수준인 단 '1'에 불과하거든요. 전기 알갱이가 외부(산화막 유전율) 힘의 영향을 받지 않고 씽씽 더 빠르게 목적지까지 도달할 수 있다는 걸 뜻합니다. 기존 공정에 비해 더 복잡한 과정이 진행되겠지만, 칩의 속도가 더욱 빨라지는 건 분명하겠네요.

TSMC, 너는 계획이 다 있구나 <2편>에서는 TSMC 패키징 기술에 관해 소개하려고 합니다. 긴 글 읽어주셔서 감사합니다. 다음 편도 기대해주세요.