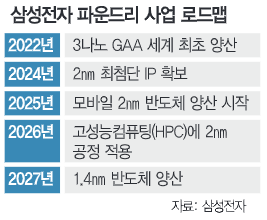

삼성전자(005930)가 세계 최초로 게이트올어라운드(GAA) 반도체를 양산한 데 이어 이번에는 첨단 소자 구조로 파운드리(반도체 위탁 생산) 혁신을 이어간다. 두 개의 GAA 소자를 수직으로 쌓아 올리는 ‘3DS-FET’라는 구조를 앞세워 파운드리 시장에서 1위 TSMC를 따라잡는다는 전략이다. 현재 대만 TSMC와 미국 인텔 등 반도체 라이벌 기업들도 이와 유사한 구조 개발에 속도를 내고 있어 향후 파운드리 경쟁력을 가르는 승부처가 될 것으로 보인다.

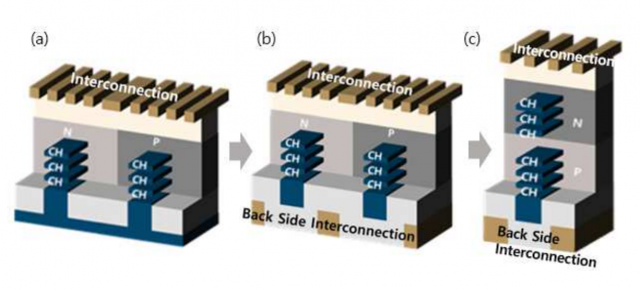

11일 업계에 따르면 최시영 삼성전자 파운드리사업부 사장은 세계적 반도체 학회인 ‘국제전자소자학회(IEDM) 2023’에서 기조연설자로 참가하면서 ‘3DSFET’ 기술과 관련한 논문을 발표했다. 3DS-FET은 지난해 6월 삼성전자가 세계 첫 양산한 3㎚(나노미터·10억 분의 1m) GAA가 한번 더 진화한 형태다. GAA는 전류가 흐르는 채널 ‘4개 면’을 게이트가 둘러싸는 구조로 기존 3개 면만 둘러싸는 핀펫(Fin-FET) 구조 대비 칩의 전력 효율성과 성능이 뛰어나다. 3DS-FET는 여기서 한 발 더나아가 성질이 다른 반도체인 n반도체와 p반도체를 GAA 구조로 만든 다음 두 개를 아파트처럼 쌓아올린 모양이다. 3DS-FET의 ‘S’는 ‘쌓는다’는 뜻의 영어 단어인 스택에서 온 말이다.

이렇게 소자를 쌓으면 동일 면적에도 최대 2배 더 많은 연산 소자를 배치해 집적도를 올릴 수 있다. 최 사장은 이 3DSFET 구조에서 전력을 효율적으로 전달할 수 있도록 칩 아래에 전력 장치를 두는 후면 ‘상호연결(backside interconnection)’ 기술을 결합할 것이라고도 소개했다.

그는 “효율적인 전압 관리로 전력을 낮출 수 있을 뿐만 아니라 칩의 부피를 줄일 수 있는 기술”이라고 언급했다. 또 “삼성전자는 3나노 GAA(MBCFET) 구조부터 스마트 시대를 위한 여정을 시작했고 삼성 파운드리는 모든 고객들을 지원할 준비가 돼 있다”고 강조했다.

3DSFET은 삼성전자만 시도하고 있는 기술은 아니다. 파운드리 라이벌 인텔도 이번 IEDM 2023 행사를 통해 GAA 소자를 수직 적층하는 기술을 차세대 핵심 기술로 내세웠다. 세계 파운드리 1위 업체 TSMC 역시 일찌감치 ‘CFET’이라는 이름으로 이 구조를 대중에게 선보인 바 있다. 이 기술은 구현 난도가 상당히 높다. 서로 다른 종류의 반도체를 수직 결합하면서 발생하는 배선 모양 변화와 공정 문제를 해결해야 한다. 그만큼 이 숙제를 먼저 풀어내는 업체에는 엄청난 기회가 주어진다. 3㎚ 이하 반도체 파운드리 시장에서 ‘빅테크’ 회사들의 마음을 사로잡을 수 있는 첨단 무기를 먼저 확보하는 것이기 때문이다.

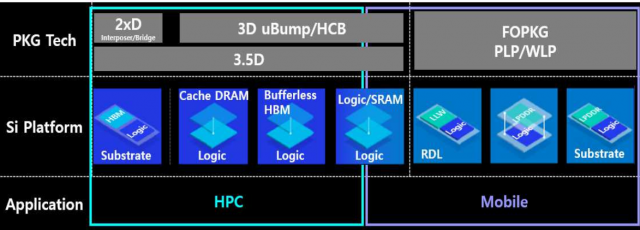

최 사장은 이번 연설에서 차세대 소자 구조 외에도 파운드리와 관련된 다양한 기술 현황을 발표한다. 특히 최근 반도체 업계에서 화두가 되고 있는 반도체 패키징에 대한 심도 있는 논의도 진행한다. 고대역폭메모리(HBM)를 연산장치 위에 얹는 방법 외에도 모바일 정보기술(IT) 기기 안에서 저지연성와이드IO(LLW) D램 등을 연산장치와 결합하는 패키징에 대한 로드맵도 공개했다.