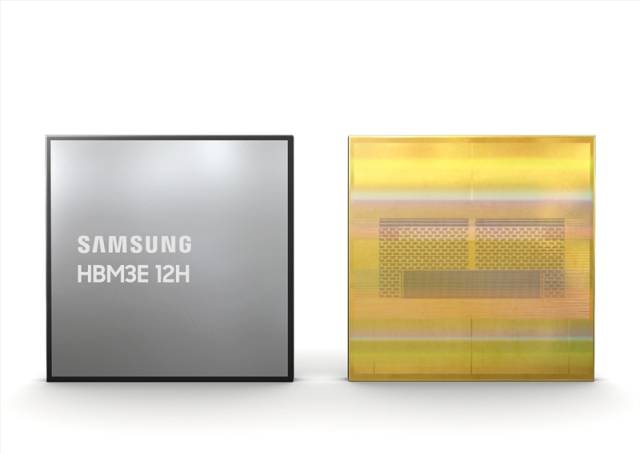

국제반도체표준협의기구(JEDEC)가 고대역폭메모리(HBM)4 표준이 완성 단계에 접어들었다고 밝혔다. HBM4는 인공지능(AI) 가속기에 필수적으로 쓰이는 HBM3e의 뒤를 이을 6세대 HBM으로 최대 16단 적층이 가능하고 더 높은 용량과 대역폭을 지원한다. 새 ‘게임의 룰’ 등장이 예고되며 HBM 시장에는 또 한 번의 변혁이 다가온다. 경쟁사 SK하이닉스·마이크론에 뒤처진 삼성전자(005930)는 HBM4를 기점으로 ‘일발역전’을 노리며 칼을 갈고 있다.

10일(현지 시간) JEDEC 솔리드스테이트 기술 협회는 “HBM4 표준이 완성에 가까워지고 있다”고 밝혔다. JEDEC이 HBM4 표준 제정 진행 상황에 관해 발표한 것은 처음이다. JEDEC은 글로벌 반도체·테크 기업이 모인 단체다. D램·낸드플래시 등 메모리 반도체는 물론 인터페이스·패키징 등 반도체 공급망 전반의 표준 규격을 만든다. JEDEC 표준은 신형 반도체 설계·제작을 위한 ‘지침서’다. 표준 완성을 기점으로 본격적인 HBM4 개발이 가능해지는 셈이다.

JEDEC은 ‘HBM4는 현재 발표된 HBM3를 넘어선 진화적 단계로 더 높은 대역폭과 더 낮은 전력소비량, 면적 당 용량 증가로 데이터 처리 속도를 더욱 향상시킨다”며 “생성형 인공지능(AI), 고성능컴퓨팅(HPC), 그래픽처리장치(GPU)와 서버 등 대용량 데이터와 복잡한 계산을 효율적으로 처리하는 데 필수적”이라고 강조했다.

이날 JEDEC은 완성 단계에 접어든 HBM4의 규격 일부를 공개했다. 성능 기준점은 기존에 알려진 것과 대동소이하다. HBM4는 12단에 머물던 HBM3·HBM3e보다 한 차원 높은 최대 16단을 지원한다. 이는 단위면적 당 용량이 커지고 속도도 더욱 빨라짐을 의미한다. D램 당 용량도 기존 최대 24Gb(기가비트)에서 32Gb로 확장된다. 층 수가 높아질 뿐 아니라 층 당 용량 밀도도 높아지는 셈이다.

또 기존 1028비트(bit)인 층 당 채널 수가 2048비트로 두 배 늘어나고 반도체 칩 면적이 더 크다는 점도 확인했다. 채널 당 속도는 6.4Gbps(초당 기가비트)로 초기 합의가 마무리됐다. 이 속도는 더 높아질 가능성이 크다. 이미 시장에 공급 중인 HBM3e가 8Gbps를 지원하고 있기 때문이다. 실제 황상준 삼성전자 메모리사업부 D램 개발실장(부사장)은 지난 3월 실리콘밸리에서 열린 ‘멤콘(Memcon) 2024’에서 HBM4 코드명 ‘스노우볼트’를 소개하며 “채널 당 속도는 8Gbps로 개발 중이지만 고객사 요청이 있다면 최대 10Gbps까지 높일 수 있다”고 밝히기도 했다. JEDEC은 “채널 당 속도에 대해서는 더 높은 주파수에 대한 논의가 계속되고 있다”고 전했다.

다만 JEDEC은 반도체 업계에서 화두가 되고 있는 적층 높이에 대해서는 언급하지 않았다. 당초 JEDEC은 올 초 HBM4 규격을 공개할 예정이었으나 적층 높이에 대한 회원사 간 이견으로 발표가 늦어졌다고 한다. JEDEC은 기존 720마이크로미터(μm)에서 775μm로 높이 제한을 완화하려는 것으로 알려져 있다. 더 높은 단 수를 쌓기 위해서는 여유 공간이 필요한 탓이다.

HBM4 규격 제정은 현재 HBM 시장에서 경쟁사에 뒤처졌다는 평가를 받고 있는 삼성전자에게 기회요소가 될 전망이다. 게임의 ‘룰’이 바뀌는 시점에서 간극을 좁힐 기회를 잡을 수 있다는 기대감이 따른다. 특히 삼성전자가 HBM에 적용중인 비전도성필름(NCF) 기술은 고적층에 유리해 ‘단수’가 16층으로 높아지는 HBM4에 최적이라는 평가를 받고 있다. 삼성전자는 더 낮은 높이로도 고적층이 가능한 하이브리드본딩 기술 개발에도 속도를 내고 있다. 지난 4월에는 하이브리드본딩을 적용해 16단 HBM4를 구현했다고 밝히기도 했다.