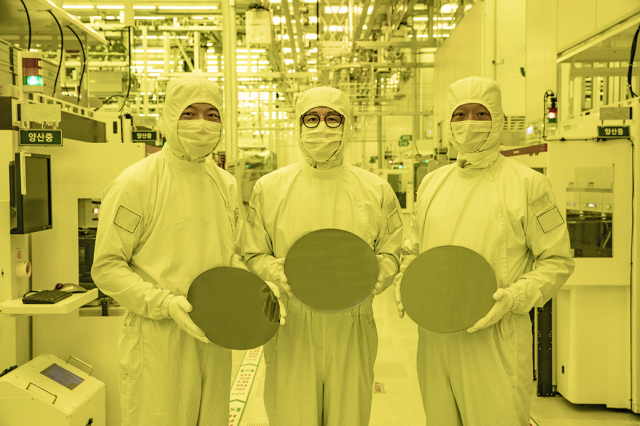

삼성전자가 대만 TSMC, 미국 인텔 등 칩 파운드리(위탁 생산) 라이벌을 제치고 3㎚(나노미터·10억분의 1m) 공정 반도체 양산을 시작했다.

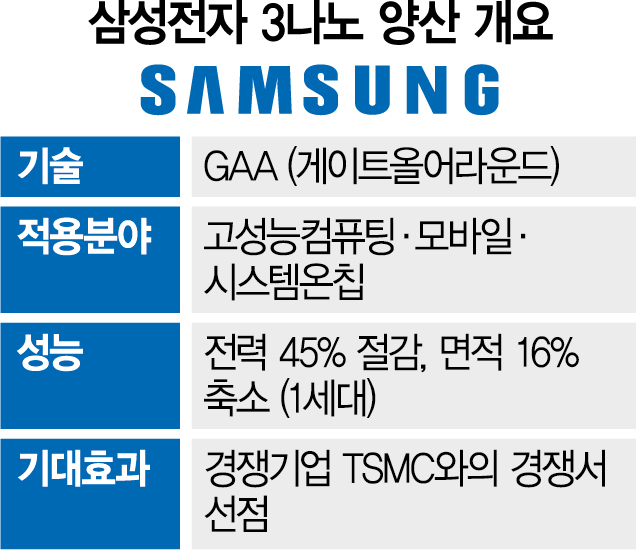

삼성전자 파운드리사업부는 이 공정을 활용해 고성능컴퓨팅(HPC)용 시스템반도체 생산을 시작했다고 30일 밝혔다. 3나노 공정으로 만든 차세대 게이트올어라운드(GAA) 기술을 구현한 반도체 회사도 삼성전자가 세계에서 처음이다.

최시영 삼성전자 파운드리사업부 사장은 “삼성전자는 파운드리 업계 최초로 고유전율(하이K) 메탈 게이트, 핀펫, 극자외선(EUV) 등 신기술을 선제적으로 도입하며 빠르게 성장했다”면서 “앞으로도 차별화한 기술을 적극 개발하고 공정 성숙도를 빠르게 높일 것”이라고 밝혔다.

이번 3나노 1세대 공정으로 GAA 트랜지스터 양산에 성공했다는 점도 큰 의미가 있다. GAA는 반도체 안에서 데이터를 처리하는 트랜지스터 구조를 혁신적으로 바꾼 기술이다. 전류 흐름을 통제하는 ‘게이트’가 전기 알갱이가 흐르는 채널을 완전히 둘러싸는 형태다. 채널의 3개 면을 감싸는 기존 핀펫 구조와 비교하면 게이트 면적이 넓어져서 데이터 처리 속도와 전력 효율을 높일 수 있다.

이와 함께 채널 모양을 넓고 얇은 ‘나노 시트’ 형태로 구현한 MBC펫 구조를 적용한 것도 괄목할 만하다. 고객사 요구에 따라 채널의 두께와 면적을 조절할 수 있는 것이 특징이다.

삼성전자는 GAA 1세대 공정으로 기존 5나노 핀펫 공정 대비 전력 45% 절감, 성능 23% 향상, 면적은 16% 축소됐다고 밝혔다. 향후 출시할 2세대 공정은 전력 50% 절감, 성능 30% 향상, 면적은 35% 축소될 것이라고 밝혔다. 업계 관계자는 “퀄컴·엔비디아·인텔 등 고객들이 삼성으로 눈을 돌릴 것”이라고 진단했다.

삼성전자는 3나노 칩을 수월하게 설계할 수 있는 다양한 디자인 솔루션을 고객사에 지원할 계획이다. 삼성전자는 삼성파운드리생태계(SAFE) 파트너인 시높시스·케이던스 등 전자설계자동화(EDA) 툴 유력 회사와 3나노 공정 반도체 설계 인프라를 제공할 예정이다.

앞으로 삼성전자는 3나노 반도체 생산량을 늘리기 위한 EUV 노광기 확보를 공격적으로 전개할 것으로 보인다. EUV 노광기는 반도체 공정 중 빛으로 회로 모양을 반복해서 찍어내는 기계다. 기존 불화아르곤(ArF) 광원보다 빛의 파장이 14분의 1 짧은 EUV로 미세 회로를 균일하고 반듯하게 그릴 수 있다.

이 기기는 네덜란드 회사 ASML이 연간 40대 안팎의 생산 능력으로 세계에서 독점 공급한다. SK하이닉스·인텔·TSMC 등 내로라하는 반도체 업체들이 장비를 먼저 확보하기 위해 치열한 경쟁을 벌이고 있다. 이재용 부회장은 14일(현지 시간) ASML 본사를 찾아 차세대 노광 장비인 하이 뉴메리컬어퍼처(NA) 장비를 자세히 살펴보고 현지 경영인과 장비 수급을 논의했다.