정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 1편에서는 유리 기판이 업계의 주목을 받게 된 이유에 대해 살펴봤습니다. 이제 본격적으로 유리 기판의 성능을 다양한 자료를 보면서 비교해보겠습니다.

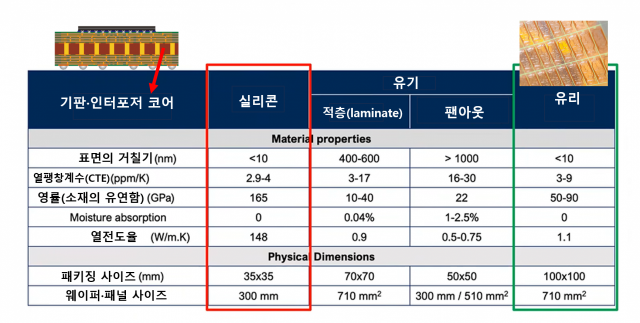

우선 일목요연하게 정리된 표를 함께 보시겠습니다. 출처는 미국 명문 펜실베니아 주립대학교의 첨단 전자 시스템 이종결합센터(CHIMES)가 만든 자료인데요. 여기서 실리콘, 유기 기판 등과 비교한 유리가 어떤 유리인지는 알수 없지만, 통상 반도체 공정에서 많이 활용되는 유리 종류인 보로실리케이트나 쿼츠 등으로 추정됩니다.

우선 표면 거칠기를 보겠습니다. 이 표면의 거칠기 수치가 작을수록 더욱 맨들맨들하고 '빤빤'한 표면을 가졌다는 말인데요. 유리의 표면 거칠기는 10㎚ 이하입니다. 실리콘의 거칠기도 10㎚ 이하네요. 반면에 유기(고분자) 기판의 거칠기는 40배에서 60배 수준인 400~600㎚입니다. 표면이 빤빤하면 1편에서도 설명드렸듯이 표면에서 미세한 회로 작업하기가 상당히 수월하다는 얘기입니다. 이른바 '파인 피치'가 가능하다는 뜻이죠. 실제 인텔은 자신들의 유리기판 성과를 소개할 때 기존 유기 기판 대비 10분의 1 미세한 회로 밀도를 구현했다고 소개했죠.

또 표면 상태가 좋으면 기판 두께 자체가 상당히 얇아질 수 있다는 장점도 있습니다. 통상 유기 기판은 표면이 거칠기 때문에 중심축인 코어 표면에서 굵은 회로부터 시작하고 층을 쌓으면서 얇은 회로를 차곡차곡 쌓아가는 형태거든요. 요즘엔 최대 20층까지 올라가거나 두께를 잡아먹는 코어를 빼버리는 방안(코어리스)도 고려됩니다. 그런데 처음부터 빤빤한 유리부터 곧바로 초미세 회로를 새길 수 있다면? 1편에서 보셨던 인터포저는 물론 중간 층이 아예 삭제돼버릴 수 있어 두께가 아주 얇아지는거죠. 축소(Scaling·Shrinking)는 반도체 엔지니어들에게 언제든 환영받을 수 있는 이슈입니다. 유리의 기대감이 올라가는 이유죠.

이제는 휨(warpage) 현상을 따지기 위해 소재의 열팽창에 대해 봅시다. 열평창계수(CTE·Coefficient of Thermal Expansion, 단위는 ppm/K)라는 걸 살펴봐야 하는데요. 일정 온도가 상승할 때마다 물질이 얼마나 팽창하면서 상태가 변하는지 보여주는 것입니다. 기판이 공정 중 발생하는 열로 인해 얼마나 휘거나 모양이 변할 수 있는지를 나타내죠. 유리의 CTE는 실리콘과 비슷한 3~9 ppm/K 입니다. 반면 유기 기판의 경우 3~17 ppm/K로 최대값이 거의 두배 수준입니다. 유리 기판이 유기 기판보다는 공정 중에 휠 우려가 훨씬 낮다는 얘깁니다. 그래서 대면적 기판의 최대 난제였던 휨 현상도 유리 기판으로 극복해볼 수 있습니다. 실제 인텔은 가로세로 24㎝ 크기 기판까지 만들어서 패키징 가능하다고 주장하고요. 조금 전 말씀드렸던 '파인 피치(fine pitch)'까지 가능하니까 같은 면적의 기판이라도 훨씬 많은 초미세 칩을 위에 올릴 수 있습니다. 한 개 기판 위에 복수의 연산 장치와 10개 이상 HBM이 필요할 것으로 예상되는 AI 시대에 안성맞춤이죠.

물체의 단단한 정도를 볼 수 있는 '영률(Young's Modulus)' 이야기도 재밌습니다. 지표가 높을수록 단단하다는 얘기인데요. 실리콘은 165GPa인 반면 유리는 50~90GPa입니다. 실리콘이 훨씬 단단하다는 뜻인데요. 이게 단단하다고 다 좋은 것은 아닌게요. 여러분 "너무 단단하면 부러진다"는 어르신들의 말씀 많이 들어보셨죠. 너무 단단하면 오히려 공정 중에 기판 소재가 깨질 확률이 크지만 말이죠. 유리처럼 적당한 유연성을 가지고 있으면 다양한 층을 붙여도 좀더 유연한 움직임이 있기 때문에 수월하게 결합할 수 있다는 거죠. 유리가 사회 생활도 잘합니다.

열 전도율(Thermal conductivity) 측면에서도 한번 따져볼게요. 이건 실리콘에 비해 150배 가까이 낮습니다. 열이 가해지면 실리콘은 모든 부분에 뜨겁고 차가운 것이 퍼지지만, 유리는 상대적으로 기복이 무딘 친구죠. 그나마 열이 전달되는 특정 부분만 잘 처리해주면 반도체 업계 최대 고민인 '열(Thermal) 관리 이슈'에서 상당히 유리해진다는 뜻입니다.

한마디로 요약을 하면 이렇습니다. 유리는 실리콘의 장점인 △빤빤한 표면 △낮은 열팽창계수는 가져가면서 유기 기판의 장점인 △낮은 열전도율과 △유연한 강도를 확보하고 있는 소재라는 거죠. 그런데 실리콘 기판이나 인터포저처럼 아주 비싼 전공정을 필요로 하지는 않으니까, 당장 개발 단계에서는 비용이 들더라도 가격 면에서 상당히 유리할 수 있다는 겁니다.

◇유리 기판 생태계가 열악한 기판 강국 코리아

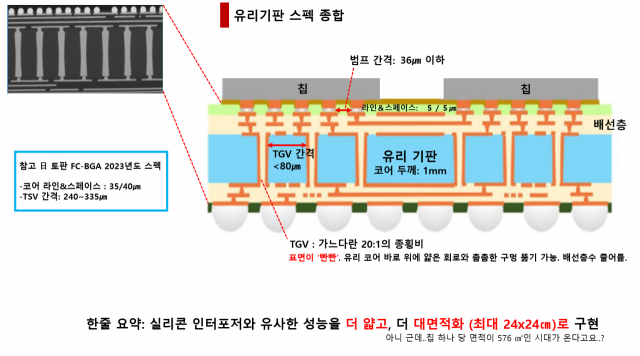

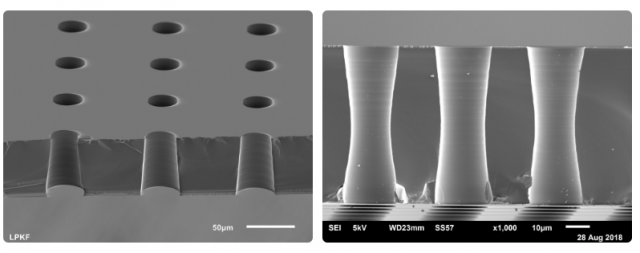

유리 기판은 완전히 새로운 형태의 기판이다보니 새로운 장비와 소재가 필요한데요. 인텔의 경우 유리 가공 장비로 상당히 유명한 LPKF, 독일 쇼트 등과 협업하는 것으로 알려졌습니다. LPKF는 실리콘관통전극(TSV)에 준하는 유리관통전극(TGV) 기술을 소개하면서 유리 기판의 가능성을 소개한 바 있죠.

미국 조지아에 월 수천패널 생산 규모의 공장을 짓고 있는 앱솔릭스의 경우 세계 최대 반도체 설계 업체 AMD가 이들에게 유리 기판 러브콜을 보내고 있다고 전해집니다. 아사히, 코닝 등 세계적인 유리 제조 업체와의 협업 가능성도 있고요. 국내 반도체·디스플레이 장비 업체 필옵틱스(161580)도 관여돼 있는 것으로 파악됩니다.

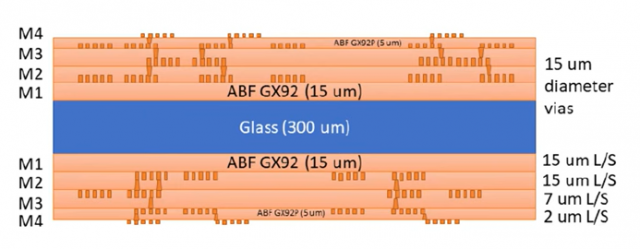

또 흥미로운 것은 글래스 기판 시대가 도래하더라도 말이죠. 기판 업계의 ‘슈퍼 을’이라고 해도 과언이 아닌 아지노모토 사가 단독 생산하는 기판용 ABF 필름의 존재감은 건재합니다. 배선층을 쌓을 때 접착제 역할을 하는 이 필름은 여전히 중용될 것으로 보입니다.

이제 기사를 마무리하면서 우리나라 유리 기판 생태계에 대해 짚고 넘어가야 할 것 같은데요. 왜 이 연재물은 맨날 결론에 생태계 얘기만 하고 끝내느냐 하실 수도 있지만, 지금 우리나라에서 두 개 대기업이 유리 기판 시장에 공식적으로 도전장을 내민 것 치곤 정말로 생태계가 열악해서 그렇습니다.

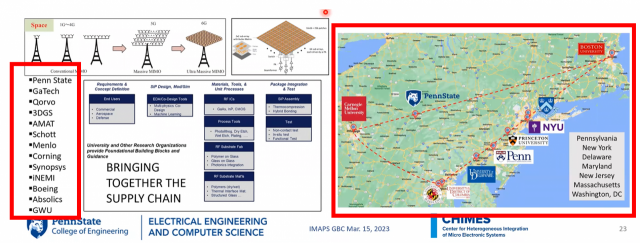

단적으로 미국과 한번 비교해볼까요. 조금 전 펜실베니아대 CHIMES를 잠깐 말씀드렸는데요. 이 센터는 펜실베니아대 혼자서만 꾸린 게 아닙니다. 뉴욕대, 프린스턴대 등 미국 동부 10개 미국 최고명문대가 함께 참여하고 있고요. 코보, 어플라이드 머티어리얼즈, 쇼트, 코닝 등 반도체 업계에서 영향력 있는 업체들도 괄목할 만한 공급망을 만들어 함께 연구를 진행하고 있습니다. 한국의 앱솔릭스도 포함돼 있죠. 미국 반도체지원법 이후 R&D 비용도 정부가 풍성하게 지원하는 것으로 보입니다. 여기서 자라난 기술과 인재들이 인텔의 유리 기판 구현을 더욱 앞당기는 거겠죠.

최근 한국에 첨단 패키징과 기판 연구 붐은 마치 패션처럼 다가왔습니다. 어느 순간부터 국내에서 '이종집적(heterogeneous integration)' 패키징이 차세대 반도체 기술로 꼽히며 갑자기 관심이 쏟아지는 건 환영할 만한 일이기는 한데요. 1970년대부터 아주 꾸준하게 패키징 분야를 연구해 온갖 고급 기술과 노하우를 섭렵한 미국과는 갖춰진 인프라와 실력이 다르다는 현실도 인지해야 합니다. 반도체 강국임을 자부하면서도 첨단 패키징 저변이 거의 전무한 수준인 국내에서 유리 기판이 빠르게 양산이 된다면 오히려 정말 엄청난 기적이 일어나는 셈이죠.

지금부터라도 유행을 따라가는 R&D 지원보다 꾸준한 투자와 독려로 관련 산학연 생태계를 지원해 기술 성공 가능성을 앞당기는 작업이 필요합니다. 김사라은경 서울과기대 지능형반도체공학과 교수는 “글로벌 첨단 반도체 패키징 분야는 상상할 수 없었던 미세 기술과 고성능으로 진화하고 있다”며 "관련 지원들이 단기적인 성과에 치중하지 않는 방향으로 마련돼야만 지속적으로 혁신적인 연구와 전문인력 양성이 가능할 것"이라고 조언했습니다.

긴 글 읽어주셔서 감사합니다. 추운 날씨 감기 조심하시고 좋은 주말 보내세요.