정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 요즘 고대역폭메모리(HBM)만큼 뜨거운 반도체 기술 이슈가 있죠. 극자외선(EUV)입니다.

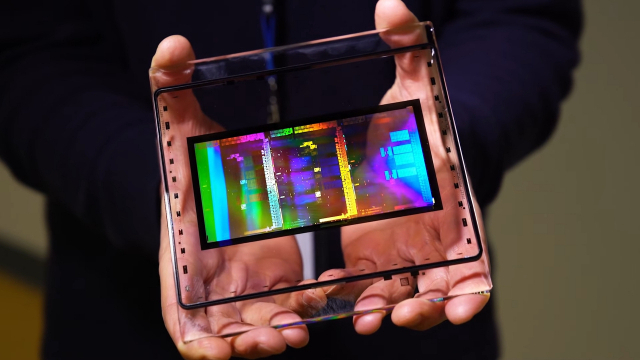

특히 우리는 인텔의 움직임을 예의주시할 만 합니다. 네덜란드 ASML의 High-NA EUV를 세계에서 가장 먼저 공급받아서 설치하면서 1나노대 파운드리를 준비하고 있습니다. 삼성전자, TSMC 등 라이벌 회사들보다 빠른 행보죠.

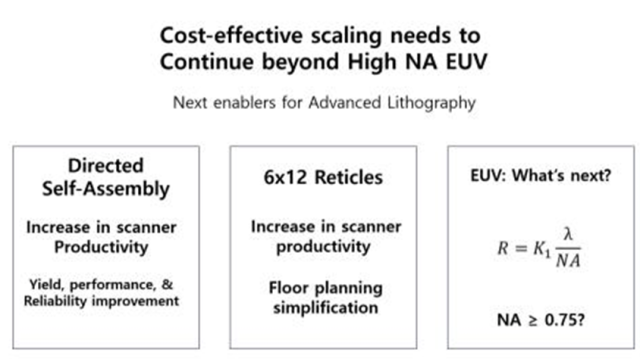

이런 가운데 인텔의 파운드리 기술 R&D를 책임지는 앤 켈러허 수석부사장이 말이죠. 몇달 전 세계 최대 광학회 SPIE 2024에서 하이-NA를 넘어서는 차세대 EUV 시대에서 대세가 예상되는 흥미로운 키워드 세 가지를 제시했습니다. △DSA △6X12인치 EUV 포토마스크 △0.75NA로 요약이 됐는데요. 오늘은 인텔이 말하는 EUV 키워드가 무엇인지, 그리고 이 기술들을 왜·어떻게 도입하려고 하는지를 자세히 살펴보려고 합니다. 그럼 DSA라는 신비로운 물질부터 출발하겠습니다.

◇하이-NA 받고, DSA로 간다

여러분, EUV 노광 공정에 대해서는 이미 수차례 들어보셨죠. EUV의 13.5나노미터의 파장을 이용해서 7나노 이하 초미세 회로를 ㅂ찍어내는 기술입니다. 하이-NA는 기존 렌즈의 크기(0.33NA)에서 1.67배 키운 0.55NA로 구현한 겁니다. 렌즈가 빛의 양을 더 많이 받을 수 있게 되면서 웨이퍼에 찍히는 회로를 더욱 선명하게 나타내겠다는 콘셉트죠.

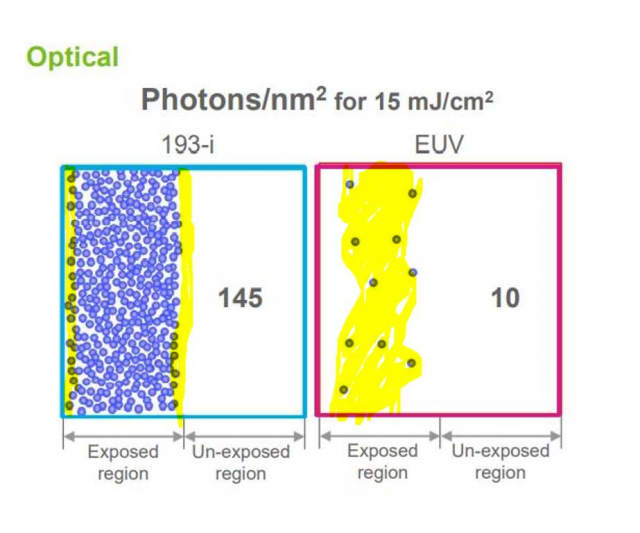

그런데 완벽해 보이는 하이-NA EUV도 몇 가지 문제가 있습니다. 가장 대표적인 문제가 '샷노이즈(shot noise)'입니다. EUV는 기존 불화아르곤(ArF) 광원보다 파장이 14분의 1이나 짧습니다. 반면에 에너지는 14배나 강하다는 특성이 있습니다. 빛의 물리적인 특성 상 동일한 에너지 안에서는 빛의 가장 작은 단위 알갱이인 광자 수가 기존의 14분의 1에 불과하다는 결론에 도달합니다. 웨이퍼에 닿는 광자 수가 턱없이 부족해서 회로 표면이 울퉁불퉁하게 찍힐 수 있다는 뜻입니다.

물론 하이-NA는 렌즈가 커지고 웨이퍼에 닿이는 빛의 양도 많아지면서 기존 EUV 기술보다 광자 수는 늘어날 겁니다. 그러나 광자 수가 증가하는 사이 세상은 지금보다 회로폭이 더 얇은 반도체를 만들고 싶어합니다. 정말 엔지니어들의 피나는 노력에도 불구하고 EUV 광자 수의 근본적인 문제는 해결하기 힘들고 회로는 더 좁아지고 있어서, 샷노이즈로 인해 생기는 예상하기 힘든 불량 회로 이슈는 더욱 심화할 것입니다.

EUV의 광자 수를 늘리기 위해 웨이퍼에 EUV를 더 많은 시간 노출시키는 방법도 고안되고 있죠. 그러나 이렇게 하면 물리적 비용과 공정 소요시간(리드타임)이 더 늘어난다는 단점이 있습니다. 1나노 이하 회로 미세화가 진행되면 웨이퍼에 빛을 조사하는 노광 공정 자체가 한계에 직면할 것이라는 우려까지 나오는 상황입니다.

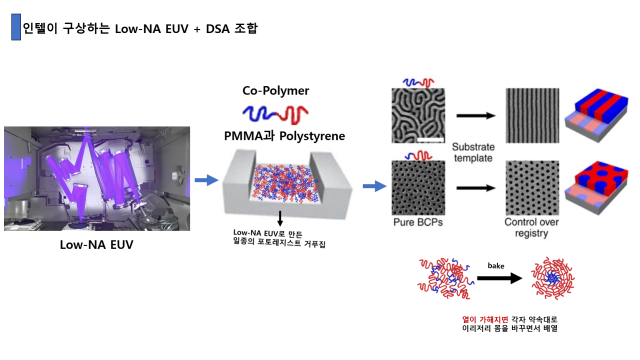

그러면서 대안으로 떠오른 개념이 DSA입니다. DSA. Directed Self Assembly입니다. 말그대로 '셀프'로 회로를 만든다는 이야기입니다. DSA는 두 개의 고분자가 한 개의 짝으로 결합된 물질, 이른바 코폴리머(Co-Polymer)를 웨이퍼 위에 바르고요. 이걸 일정 온도로 가열을 하면 두 개의 고분자들이 스스로 자리를 찾아가면서, 엔지니어들이 의도한 대로 회로 모양을 만들어나가는 아주 신비한 기술을 일컫습니다.

이 DSA 작업만 놓고 봤을 때는 빛 없이도 웨이퍼 위에 용액을 바르고 가열하면 패터닝이 가능하다는 건데, 샷 노이즈를 배제할 수 있는데다, 심지어 더 정교하게 회로를 만들 수 있으니 너무 장점이 명확하다는 거죠. 이 코-폴리머 물질의 강력한 후보로는 폴리메틸 메타크릴레이(PMMA)와 폴리스타이렌(polystyrene)의 결합이 거론됩니다.

그러면 인텔은 EUV 노광에 어떻게 DSA를 활용하려고 할까. 하이-NA와 함께 DSA를 동시에 활용하는 것은 비용이 너무 많이 든다는 문제가 있습니다. 그도 그럴 것이 하이-NA 장비 하나가 5000억원을 훌쩍 넘기는데 유지 비용도 어마어마하겠죠.

그래서 인텔이 고안하고 있는 최선의 방법은 기존 로우-NA(0.33NA)와 DSA의 결합입니다. 그러니까 기존 EUV 노광기로 포토레지스트 위에 고분자 용액이 들어갈 일종의 거푸집(탬플릿)을 만들어준 후, 여기에 코폴리머 물질을 채우고 가열해 패턴을 만든다는 거죠. 통상 지금까지 EUV 노광은 반도체의 각 층을 연결하는 얇은 구멍(Via)을 뚫을 때 활용해왔는데요. DSA 역시 이 분야에서 아주 요긴하게 쓰일 것으로 전망됩니다.

DSA를 예전부터 아주 열심히 연구하면서 강하게 드라이브를 걸고 있는 화학소재 기업은 독일의 머크입니다. 인텔이 DSA의 가능성을 언급하고 있는 가운데, 머크가 DSA를 구현해서 하이-NA 시대에서 큰 성과를 볼 수 있을지 기대해봐야겠습니다.

◇하이-NA, 포토마스크 생태계를 뒤집을까

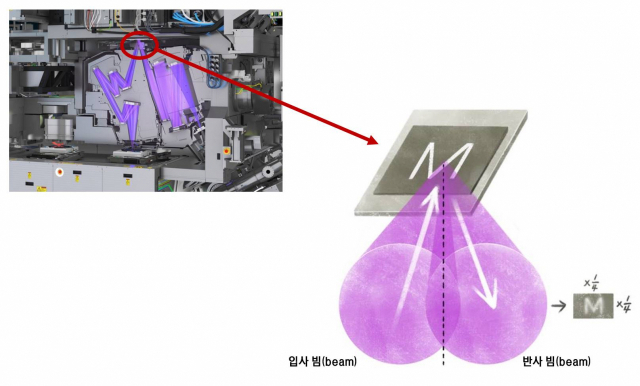

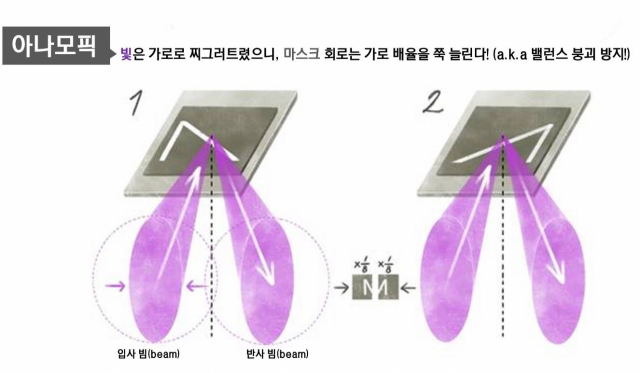

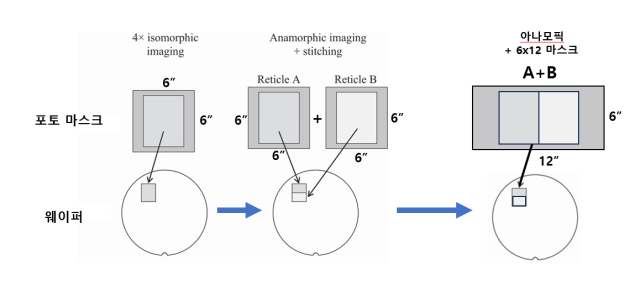

인텔은 두번째 이슈로 ‘6X12 포토마스크’에 대한 이야기를 꺼냈습니다. 왜 이 화두를 던진걸까. 여러분, 제가 작성했던 지난 하이엔드 테크 기사의 <하이-NA> 편을 보시면 '아나모픽'에 관한 이야기가 등장합니다. 0.55NA EUV 시대가 되면서 빛의 양이 많아졌고, 회로 모양을 머금기 위해 닿여야 하는 포토마스크 부분에서 입사빔과 반사빔이 겹치면서 문제가 생긴다는 설명을 드렸었죠.

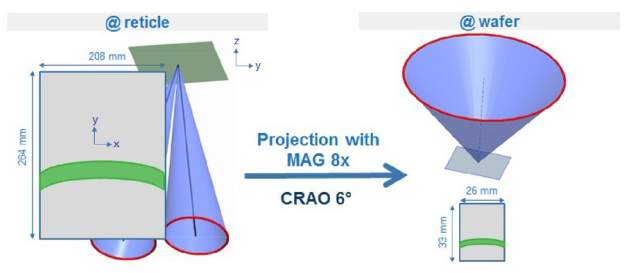

그러면서 입사빔과 반사빔이 서로 닿이지 않게끔 찌그러뜨릴 수밖에 없었고, 빔을 찌그러뜨린만큼 마스크의 회로도 길쭉하게 늘려서 밸런스 붕괴를 막는다는 말씀도 함께 드렸습니다. 또 포토 마스크를 길쭉하게 늘린 대가(?)로 회로를 한 노광에 딱 절반만 찍어낼 수 있었고, 하이-NA 시대에 가면 반반씩 노광을 해서 하나로 이어붙이는(stitching) 공정이 구현된다는 이야기도 드렸습니다. 여러분, 그런데 최대한 간략하게 설명을 해도 직관적이지 않고 장황하지 않나요. 그만큼 이 하이-NA와 아나모픽 구현이 단계가 많고 만만하지 않다는 이야기입니다.

그럼 빛의 사이즈가 커진만큼 포토마스크도 커지면 안될까. 맞습니다. 실제 과거 하이-NA를 구현할 때 그런 방안이 논의가 됐습니다. 가장 심플한 방법이기도 하니까요.

문제는 생태계입니다. 만약 이 생태계가 인텔의 생각처럼 아주 갑자기 바뀌어버린다면 한바탕 난리가 날 것입니다. EUV 노광기 안에는 수만 개의 부품이 들어갑니다. 포토마스크 크기가 변하는 순간 ASML의 각 공급사 생산 라인은 일대 변화가 일어날 것이고 EUV용 블랭마스크를 생산하는 일본 호야 등 각종 핵심 소재 회사들의 공급망관리(SCM)는 처음부터 사업 전략을 다시 짜야할 겁니다.

인텔의 6x12인치 포토마스크의 컨셉은 이러한 생태계와 맞딱드린 기술 문제를 동시에 해결하기 위한 절충안으로 보입니다. 현재의 가로 세로 6인치 정사각형 EUV 포토마스크의 한 쪽 부분의 길이만 기존의 두 배로 늘리는 방안이죠. 가로와 세로 길이 모두 늘리지 않고 한 쪽만 늘려서 아나모픽 기술 유지와 함께 나타날 생태계의 혼란을 최소화하고, 인텔이 원하는대로 한 방에 회로를 찍어낼 수 있는 방법을 제시한거죠.

실제 인텔이 이 문제를 ASML에 협조를 요청했고, 6인치 EUV 포토마스크를 두 배 크기로 키우는 게 어떻겠느냐는 제안을 ASML 역시 진지하게 고려를 하고 있다는 전언이 들립니다.

인텔과 ASML이 이 문제에 대해 어떤 결정을 할지, 또 이 결정이 삼성전자와 SK하이닉스, TSMC가 갖추게 될 하이-NA 라인에는 어떤 영향을 미칠 지 지켜봐야 할 부분입니다.

◇EUV는 0.55NA까지? 아니, 0.75NA도 준비 중

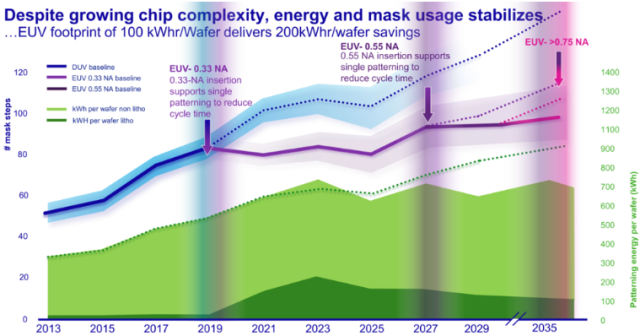

인텔이 이 슬라이드에서 마지막으로 언급한 키워드는 0.75NA입니다. EUV 노광 렌즈의 크기를 0.55NA에서 멈추지 않고, 0.75NA까지 또 한번 늘려보겠다는 거죠. 사실 이 이슈는 ASML이 수차례 언급한 이슈이기도 합니다. ASML은 2035년 이후 0.75NA를 구현할 수 있을 것이라고 주장한 적이 있습니다.

인텔은 요즘 ASML과의 긴밀한 협조로 최첨단 0.55NA EUV 장비를 세계에서 가장 먼저 확보하고 있죠. 앞으로 인텔이 0.75NA 장비에 대한 연구를 얼마나 빠르게 진행할지가 반도체 제조 업계의 중요한 변수로 작용할 것 같습니다.

인텔의 앤 켈러허 수석 부사장의 발표로 살펴본 인텔의 EUV 전략과 트렌드는 여기까지입니다. 다음은 인텔의 패키징 전략에 대해 살펴보려고 합니다. 즐거운 주말 보내세요.