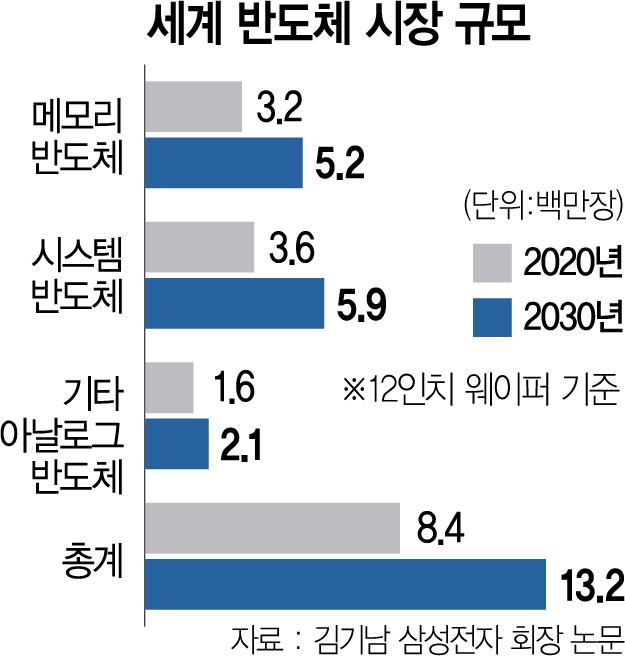

김기남 삼성전자 종합기술원 회장의 이번 발표에는 미래 반도체 시장에서 반도체 ‘초격차’를 노리는 삼성전자의 비전이 엿보인다는 평가가 나온다. 새로운 D램 패러다임이 될 3차원(3D) D램 소개와 1,000단 이상 낸드플래시 구현은 물론 2나노 이하 최첨단 공정과 패키징 기술로 외연을 넓혀 시스템 반도체 1위를 겨냥한다는 삼성전자의 전략도 고스란히 녹아들어 있다는 분석이다.

◇3D D램 원천 기술로 미래 시장에서도 독보적 ‘선두’ 확보=3D D램은 D램 시장의 패러다임을 완전히 바꾸는 기술이다. 3D D램의 핵심 키워드는 ‘트랜지스터 적층’이다. 현존하는 2D D램은 전기신호 스위치 역할을 하는 트랜지스터(소자) 수백억 개를 단 한 개 면에만 배치한다. 면적을 최소화해 한 면에 더 많은 트랜지스터를 욱여넣는 것이 과제다. 그러나 소자 미세화 기술이 한계에 봉착했다는 지적이 업계 곳곳에서 나오고 있다.

이 문제점을 해결하기 위해 등장한 콘셉트가 3D D램이다. 3D 낸드플래시에서 정보를 저장하는 ‘셀’을 100층 이상 쌓는 것처럼 D램 소자도 이런 방식으로 쌓아 집적도를 극대화할 수 있다. 전문가들은 이 기술이 오는 2025년 이후 본격적으로 구현될 것으로 보고 있다. 그럼에도 김 회장이 3D D램 기술을 언급한 것은 현재 D램 시장뿐 아니라 미래 D램 시장에서도 원천 기술을 바탕으로 독보적인 1위를 차지하겠다는 의지를 나타낸 것으로 해석된다.

◇1,000단 이상 낸드로 ‘원조’ V낸드 자존심 이어가

최근 176단 3D 낸드 양산에 들어간 삼성은 미래 기술 선점에도 박차를 가하고 있는 것으로 보인다. 이번 발표에서 김 회장은 “삼성전자는 기술과 소재 혁신을 통해 1,000단 이상 낸드플래시 기술도 구현할 수 있을 것으로 기대하고 있다”고 말했다.

삼성전자는 지난 2017년 낸드플래시 핵심인 ‘채널 홀’을 균일하고 미세하게 뚫는 회사 독자 기술 ‘9홀(hole)’을 발표한 적이 있다. 김 회장은 이번 발표에서 이 기술을 업그레이드한 ‘14홀’ 기술을 소개했다. 또 그는 앞으로 낸드플래시 주변 회로를 기존과 달리 아예 따로 만들어서 결합하는 ‘웨이퍼 본딩’ 기술, 한 개의 저장 공간에 네 개의 비트를 저장하는 쿼드레벨셀(QLC)을 뛰어넘는 기술에 주목해야 한다고 언급했다.

◇2나노 3D 적층 트랜지스터 소개…2030 파운드리 1위 정조준

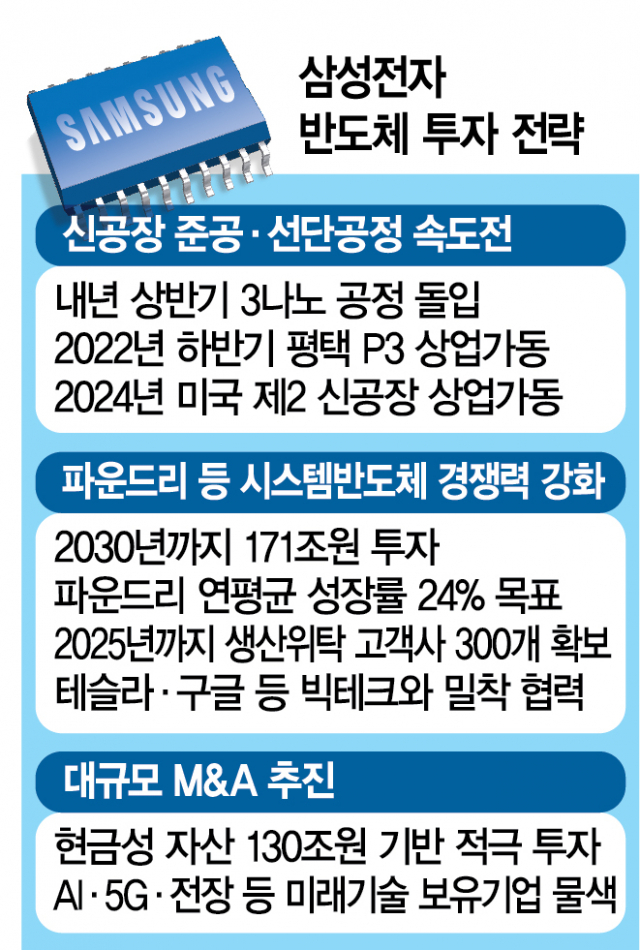

파운드리 분야에서는 2나노 이하 공정 기술을 소개했다. 그는 트랜지스터를 3차원으로 쌓아올리는 ‘3D 적층 트랜지스터(FET)’를 예로 들었다. 삼성전자는 내년 상반기 세계에서 처음으로 3나노 게이트올어라운드(GAA) 공정을 파운드리 공정에 도입하는 등 최첨단 공정 선제 도입을 통해 파운드리 1위 기업 TSMC의 뒤를 바짝 쫓고 있다.

삼성전자는 3나노 공정을 넘어 2나노 공정 로드맵을 속도감 있게 구현하기 위해 다양한 모양의 최첨단 트랜지스터를 개발하고 있는 것으로 보인다. 이를 기반으로 퀄컴·IBM 등 5나노 공정을 활용하고 있는 초대형 칩 설계 회사와의 공고한 협력 관계는 물론 칩 내재화를 노리는 세계적인 정보기술(IT) 회사들의 요구 사항에 맞출 수 있는 최적의 파운드리 인프라를 구축할 것으로 예상된다. 김 회장은 “삼성은 7나노 이하의 복잡한 회로를 EUV 공정을 통해 구현하고 있다”고 밝혔다.

◇차세대 ‘초격차’ 시동 거는 삼성…차세대 공정 개발팀까지 갖춰

업계에는 삼성이 메모리 시장에서 독보적인 선두 유지는 물론 파운드리 시장에서 라이벌인 대만의 TSMC를 제치고 1위를 차지하기 위해 공격적인 연구개발(R&D) 투자를 진행할 것으로 예상하고 있다.

이미 이달 삼성전자가 단행한 조직 개편에서는 차세대 칩 양산을 위한 차세대공정개발팀이 반도체 연구소 내에 갖춰졌다. 이번에 부사장으로 승진한 메모리제조센터 출신의 이종명 부사장이 이 조직을 총괄한다.

한편 김 회장은 이번 발표에서 글로벌 반도체 시장 혁신을 위한 의견도 제시했다. 그는 △반도체 인력 양성 △친환경 반도체 개발 △국제적 반도체 협력 등을 반도체 혁신의 세 가지 축으로 내세우며 상당히 중요하다고 주장했다. 특히 각국의 자국우선주의 기조보다는 유연한 공급망 협력으로 폭증하는 반도체 수요에 대응해야 한다는 그의 의견도 주목을 끈다. 김 회장은 “글로벌 공급망 리스크가 계속된다면 칩 가격이 상승하면서 각종 전자제품의 가격도 오를 수밖에 없다”고 밝혔다.