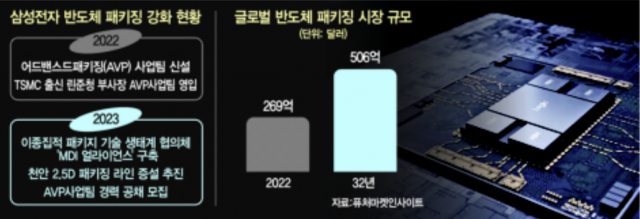

삼성전자(005930)가 반도체 첨단 패키징(후공정) 사업 강화를 위해 인력 수혈에 나서는 등 투자를 빠르게 확대하고 있다. 패키징은 반도체 칩을 탑재할 기기에 맞는 형태로 만드는 기술 및 공정을 총괄하는 개념이다. 인공지능(AI)과 고성능컴퓨팅(HPC)용 고성능 반도체 제조에서 첨단 패키징 기술력이 주목받으면서 경쟁력을 끌어올리겠다는 의도로 풀이된다.

AVP사업팀 신입 이어 경력 충원

1일 업계에 따르면 삼성전자 반도체(DS)사업부는 이달 9일까지 진행하는 경력 사원 채용을 통해 어드밴스드패키징(AVP)사업팀 인력을 충원한다. 삼성전자는 지난해 말 AVP사업팀을 조직한 후 올해 3월 AVP사업팀 반도체 공정 기술, 패키징 개발, 설비 기술 등의 부문에서 신입 공채를 진행했다. 넉 달 만에 추가 인원을 모집하며 조직 규모 확대에 나선 것이다.

이번 채용에는 △반도체 재료 개발 △어드밴스드패키지 설계 △이종 집적(Heterogenous Integration) 기술 개발 △패키지 단위 공정 개발 등의 직무가 포함됐다. 공고에서는 FOWLP(Fan Out Wafer Level Package), 실리콘관통전극(TSV) 등 다양한 패키징 기술명이 거론됐다. 패키징 단위 공정 직무에서는 차세대 제품 로드맵 기반 요소 기술, 한계 극복 기술 개발을 위해 고대역폭메모리(HBM) 등 AI향 메모리 제품을 중심으로 2.5D 패키징 공정 경험을 5년 이상 보유해야 한다는 점을 필요 역량으로 명시했다. 반도체 수탁생산(파운드리)-메모리-패키징을 결합한 ‘턴키’ 서비스에 승부수를 둔다는 삼성전자의 전략이 엿보이는 대목이다.

미세공정 한계 넘어 후공정 강화…"TSMC 추격 발판"

삼성전자는 올해 들어 눈에 띄게 빠른 속도로 반도체 패키징 사업 강화에 힘쓰고 있다. HBM 양산 확대를 위한 2.5D 패키징 라인 증설을 추진하고 있고 일본 요코하마에도 첨단 패키징 개발 거점을 설치할 계획이다. 하반기에 들어서는 전자설계자동화(EDA), 설계자산(IP), 기판 테스트 분야 파트너와 함께 이종 집적 패키지 기술 생태계를 만들기 위한 협의체 ‘MDI 얼라이언스’도 구축하고 있다.

최시영 삼성전자 파운드리사업부장(사장)은 지난달 초 파운드리 포럼에서 “2025년에 게이트올어라운드(GAA) 공정으로 만든 칩을 3차원(D) 패키징에도 확대 적용할 것”이라며 차세대 패키징 기술 로드맵을 직접 밝히기도 했다. 그러면서 “미세화 공정으로는 비용 절감과 칩 면적 축소에 한계가 있기 때문에 첨단 후공정 제품군을 다양화하고 있다”고 강조했다.

과거 반도체 패키징은 기술 난도가 높지 않고 과정이 단순해 외주를 맡기는 경우가 많았다. 그러나 초미세공정 기술이 10㎚(나노미터·10억분의 1m) 아래로 진입하고 미세화 기술이 한계에 도달하며 상황이 달라졌다. 패키징 기술 진화로 같은 선폭에서도 더 뛰어난 성능의 반도체를 만들 수 있기 때문이다. 서로 다른 칩을 이어서 마치 한 개의 반도체처럼 움직이게 하는 방식이다.

삼성전자뿐 아니라 대만 TSMC와 SK하이닉스(000660) 등 반도체 업계도 반도체 패키징 사업 강화에 적극적으로 임하는 모습이다. 패키징 분야에서 상대적으로 우위를 차지하고 있는 TSMC는 최근 자국에 3조 7000억 원을 투자해 첨단 반도체 패키징 공장을 짓기로 했다. SK하이닉스도 내년 양산 예정인 차세대 HBM을 위해 TSV 공정 생산능력 확보 투자를 검토하고 있다.