정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 인공지능(AI) 시대가 열리면서 반도체의 모양·성능도 정말 다양하게 변하고 있죠. D램 구조도 각양각색으로 바뀌고 있습니다. 대표적인 제품이 HBM이죠.

그런데 오늘은 그간 많이 다뤄졌던 HBM 외에도 독특하게 고안된 반도체 장치들을 들여다 보려고 합니다. 삼성전자가 세계적인 반도체 설계 학회 'ISSCC 2024'에서 보여줬던 D램 계층별 새로운 제품에 대해 구체적으로 살펴보고 삼성의 접근 방식을 탐구하려고 합니다. 이번 시리즈에서 콕 집어본 장치는 △LLW △GDDR △HBM-PIM 입니다. 먼저 LLW 콘셉트부터 보시겠습니다.

■LLW: AR 시대에 대응하는 새로운 무기

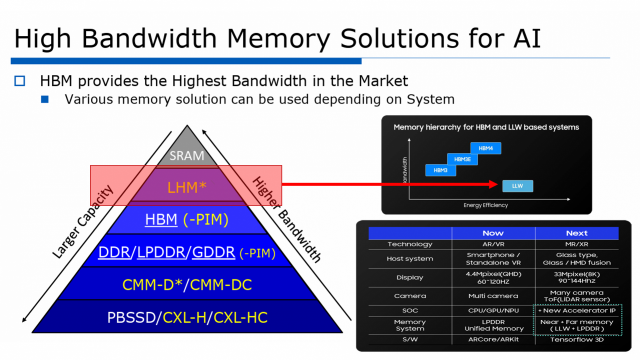

LLW D램. Low Latency Wide I/O 의 줄임말입니다. 어려워보이지만 뜯어보면 쉽습니다. 이 D램을 딱 한마디로 요약하면요. 온디바이스 AI 기기를 위한 용량 작은 고대역폭메모리(HBM)입니다.

독자님들, HBM의 역할은 너무나 잘 알고 계시죠. 서버 등 고성능 컴퓨팅 기기(HPC)용 연산 장치 옆에 딱 붙어서 연산 속도를 극대화하는 D램인데요. 범용인 DDR D램 모듈보다 탑재 위치가 가깝고 데이터 전송 속도(대역폭·Bandwidth) 면에서 큰 장점이 있어 하이퍼스케일 데이터 연산 장치로 각광받고 있습니다.

그런데 AI는 서버를 벗어나 점점 우리 손바닥 위에서도 구현이 되고 있죠. 우리가 손에 들고 다니는 노트북 PC·스마트폰·최근 뜨고 있는 증강현실(AR)·가상현실(VR) 헤드셋이나 스마트 안경 등도 폭증하는 데이터를 연산해 AI를 보여줘야 합니다. 전자 기기에 주로 탑재되는 LPDDR D램 모듈로는 우리가 원하는 만큼의 AI 연산 속도를 구현할 수 없다는 문제에 봉착하게 됩니다.

그래서 나온 개념이 LLW D램입니다. 기존 LPDDR D램보다 정보 출입구(I/O) 수를 대폭 늘려 데이터 이동 통로를 늘린 것이 특징이고요. 이 D램의 위치는 AI 반도체나 그래픽을 처리하는 칩 바로 옆에 붙어서 지근 거리에서 연산을 돕습니다.

그런데 이 콘셉트 어디서 많이 들어본 것처럼 상당히 익숙하시죠? 맞습니다. 이미 비슷한 형태의 D램이 상용화된 사례가 있습니다. 애플의 AR 헤드셋 '비전 프로'에 탑재된 SK하이닉스의 커스텀 D램입니다. 비전 프로 안에서 각종 외부 정보를 받아들여서 연산하는 'R1' 칩 바로 옆에 탑재가 된 D램인데요. 기존 LPDDR D램보다 입출구(I/O)수를 무려 8배 많은 512개를 뚫은 게 특징입니다.

삼성전자 자료를 보면 LLW D램을 SK하이닉스의 커스텀 D램과 상당히 비슷하게 접근한 모습입니다. HBM에서 했던 것처럼 실리콘관통전극(TSV)을 활용해 입출구(I/O)를 만들었을 것으로 추정되고요.

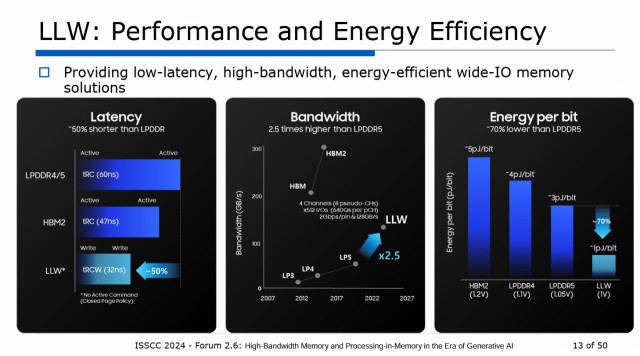

SK하이닉스의 커스텀 D램과 같은 I/O 수를 구현해서 LPDDR5 D램보다 2.5배 높은 초당 128기가바이트(GB) 대역폭을 구현했습니다. 덕분에 데이터 지연성(latency)은 LPDDR D램의 절반 수준이어서 병목 현상을 빠르게 해결한 모습이고요. 전력 효율도 좋습니다. LPDDR 칩이 비트당 3피코줄(pJ) 안팎의 전력을 소모하는 것에 비해 LLW D램은 동일 조건에서 70%나 줄어든 비트 당 1pJ을 구현한다고 합니다. 앞으로 삼성전자가 어떤 고객사에 LLW D램을 공급하게 될 지를 지켜보는 것도 D램 시장에서의 관전 포인트가 될 것 같습니다.

■GDDR7 : I'm Still Alive

다음은 GDDR입니다. 말그대로 그래픽용 DDR 규격의 D램입니다. 한동안 HBM의 강세에 GDDR은 기가 죽은 것처럼 보였죠. 그래픽처리장치(GPU)가 중용되는 AI 시장에서 대역폭과 용량이 '생명'이 되면서, GPU 옆엔 GDDR보다 HBM이 붙어있는 게 더 효율적이라는 프레임과 평가가 나온 뒤부터였는데요.

그래도 GDDR. 아직 살아있고 쓰임새도 많습니다. 하이퍼스케일 이외의 좀 더 로우엔드(low-end)의 AI 시장에서는 HBM 대신 저렴한 GDDR을 쓸 여력이 남아있고요. 점차 게임기·VR 디바이스 역시 진화에 진화를 거듭할 것이기에 GDDR 성능과 시장 수준도 고도화가 예상됩니다. 세계 GDDR 시장 매출은 2018년 32억 달러 규모에서 2030년 48억 달러까지 증가할 것으로 예상되죠.

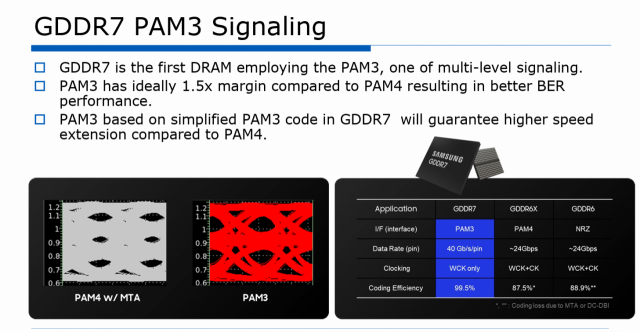

최근 세계 반도체표준협회인 국제반도체표준협의기구(JEDEC)에서도 차세대 GDDR7 D램에 대한 표준을 공식화하며 화제가 됐습니다. I/O 당 최대 속도를 초당 48Gb로 규정하고 PAM3 신호 방식을 처음으로 채택했다고 한 게 가장 눈에 띄죠.

삼성전자는 GDDR7 D램에 대한 자신감이 있습니다. 지난해 7월 입출구 당 32Gb, 그러니까 1초에 320억 개의 0또는 1을 전송할 수 있는 초고속 D램을 세계 최초로 개발했죠. 조금 전 설명드린 LLW D램의 한 개 입출구 당 데이터 전송 속도가 2Gb·삼성전자 12단 HBM3E 속도가 초당 10Gb인 걸 고려하면 엄청난 속도입니다.

삼성전자는 ISSCC 발표에서도 GDDR7의 장점을 설명했는데요. 지난해 개발 완료 발표 당시의 초당 32Gb 속도보다 한층 업그레이드 된 초당 40Gb 속도를 제시하기도 했고요. 특히 PAM3 신호 방식으로 전세대인 GDDR6·GDDR6X 제품에서 썼던 PAM4나 PAM2(NRZ·Non Return to Zero) 신호 방식에 비해 더욱 개선된 스피드를 구현할 수 있다고 소개했습니다.

여기서 우리에게 조금은 생소한 개념인 PAM을 조금 더 살펴보면요. PAM은 펄스 진폭 변조(Pulse Amplitude Modulation)의 줄임말입니다. 반도체가 데이터 신호를 받아들이거나 외부로 전달할 때는 마치 맥박이 뛰는 것처럼 주기(사이클)가 있는데요. 한 맥박이 뛸 때, 그러니까 한 사이클마다 몇 번의 변조를 주면서 데이터를 전송할 수 있는가를 정한 일종의 규칙이 PAM입니다. 즉 PAM3는 한 주기(사이클)마다 3개·PAM4는 4개의 단계(level)로 나눠서 데이터를 전송할 수 있는 방법입니다.

그렇다면 PAM4는 한 사이클마다 더 많은 데이터를 전송할 수 있을테니 좋은 것 아니냐고 물을 수 있을텐데요. 일종의 '과유불급'이랄까요. PAM4는 다양한 변조가 가능한 대신 외부 간섭 현상에 취약하다는 단점 때문에 오히려 데이터 전송 오류가 더 많이 발생할 수 있다고 합니다. 그래서 GDDR7은 NRZ와 PAM4를 절충한 PAM3를 채택한 것으로도 보이는데요.

실제 삼성의 자료에서도 보면 PAM3의 코딩 효율(Coding Efficiency)은 PAM4 신호 방식을 썼을 때보다 11.5%나 올라갔다고 설명했습니다. 삼성 자료에서도 "PAM3를 쓰면 PAM4에 비해 비트오류율(BER)이 개선돼 1.5배 더 나은 성능을 기대할 수 있다"며 "PAM4보다 PAM3 신호 방식이 속도 확장을 더 보장할 것"이라고도 덧붙였죠.

지금까지 삼성의 LLW와 GDDR7 D램 성능에 대해 알아봤는데요. 2편에서는 삼성이 PIM(Processing-In-Memory) 기술을 차세대 메모리에 어떻게 적용하는지를 알아보겠습니다. 좋은 주말 보내세요.