[이달의 과학기술자상] 최양규 카이스트 전자전산학과 교수<br>손톱크기만한 고집적 칩에<br> DVD 1,250장 저장 가능<br>시장규모 200兆달할듯

'무어의 법칙 종언을 선언한다.'

실리콘을 소자로 한 반도체 산업은 지난 30년 동안 반도체 칩의 속도는 18개월마다 두 배가 빨라진다는 '무어(인텔 창업자)의 법칙'에 지배를 받았다. 그러나 해가 갈수록 소자의 소형화 경향으로 인해 업계에서는 실리콘 소자의 한계는 어디고 언제 끝나느냐는 즉, 무어의 법칙의 종료 시점이 언제냐에 관심이 쏠려왔다. 그만큼 실리콘 소자를 통한 반도체 칩의 속도나 소형화에는 한계가 있다는 것을 반도체 업계 스스로 인정하고 있던 셈. 다만 시기가 문제였던 셈이다.

업계의 이 같은 궁금증을 말끔히 해소한 것은 6월 '이 달의 과학기술자상'을 수상한 최양규 한국과학기술원(카이스트) 전자전산학과 교수의 몫이었다. 최 교수가 개발한 세계 최소형 3나노급 나노전자소자(FinFET) 연구성과는 업계의 실리콘을 이용, 5나노급보다 적은 칩은 개발할 수 없을 것이라는 통설을 뒤집었다. 현재 생산되고 있는 실리콘 칩은 65나노급인 만큼 3나노급 칩의 생산은 반도체 기술의 한 획을 긋는 셈이다.

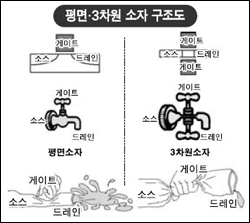

◇FinFET 소자구조 이용, 3나노 실리콘 소자 구현= FinFET는 'Fin(물고기의 지느러미)+FET(Field Effect Transistor)'의 합성어다. 물고기의 지느러미 모양을 이용, 전류가 흐르는 통로를 3차원으로 세우고 게이트가 이 통로를 다중으로 감싸고 있는 트랜지스터의 구조다.

FinFET구조는 최 교수가 소속됐던 미국 버클리대에서 99년 처음 개발한 3차원 소자구조다. 소자의 소형화로 인해 극소형 트랜지스터가 가지고 있던 전류 누설 문제를 해결하는 데 가장 탁월한 것으로 평가를 받고 있다.

이는 FinFET이 2차원 평면 소자구조 크기를 작게 하는 데 한계로 알려진 단채널 효과를 줄이고, 작동전류의 크기를 증가시키기 위해 물고기 지느러미처럼 수직으로 형성된 얇은 채널을 2개 이상의 게이트로 제어함으로써 채널에 대한 게이트의 영향력을 확대시키면서 가능하게 됐다.

이에 따라 FinFET는 초소형 고집적 반도체를 만들기 위한 유망 기술로 평가를 받으면서 삼성전자ㆍIBM 등 세계적인 반도체 기업이 앞 다투어 실용화시키기 위해 연구하고 있는 상황이다.

FinFET이론을 이용할 경우 한계로 인식됐던 3나노 실리콘 반도체 칩을 만들 수 있다. 이 이론을 바탕으로 세계에서 가장 작은 3나노급 소자를 개발, 실리콘반도체의 한계를 극복할 수 있게 된 것. 삼성전자 등 반도체 기업들은 갈륨, 탄소 등 새로운 소재에 대한 개발 부담을 덜고, 앞으로 20년간은 실리콘을 이용, 더 속도가 빠른 반도체 칩을 생산할 것으로 기대하고 있다.

◇3나노급 반도체의 위력= 3나노급 반도체 칩의 위력은 상상을 초월한다. 손톱만한 칩에 성인 머리카락 두께의 4만분의 1 크기로 설계된 트랜지스터가 집적된다. 탑을 쌓듯이 트랜지스터를 집적해 손톱만하게 만들어 목걸이에 걸고 다닐 경우, DVD 1,250장, 1만2,500년 분의 신문기사, 50만곡의 MP3 파일을 저장할 수 있다.

3나노 소자로는 D램, S램, 플래시 메로리 등의 소자로도 활용이 가능하다. 칩으로 개발할 경우 기상 예측정도의 슈퍼컴퓨터 속도는 아니지만 게임, 3차원 사이버스페이스 등을 구현할 때, 거의 현실에 가깝게 나타낼 수도 있을 정도다.

3나노 실리콘 칩이 지니는 경제적 효과도 엄청나다. 기업으로써는 실리콘 소자의 뒤를 이을 새로운 재료, 즉 탄소ㆍ갈륨 등에 대한 연구 부담이 상대적으로 덜게 됐다. 최소 실리콘을 가지고 20년은 더 반도체 칩을 생산할 수 있기 때문. 더구나 3나노급 칩을 갈륨 등으로 만들 경우 가격도 최고 100배나 비싸 대중성이 떨어진다는 설명이다.

실리콘 소자를 이용한 3나노급 칩의 시장 규모는 200조원에 달할 것으로 예측되고 있다. 이는 2015년 반도체 시장의 규모가 500조원이고 이중 극소형트랜지스터가 차지하는 비중이 40%로 볼 때 200조원에 달할 것으로 전망된다.

● 반도체 소자기술, 정부 체계적 지원 필요"

최양규 카이스트 전자전산학과 교수

"3나노급 반도체 소자를 개발할 수 있다는 가능성은 학계보다는 산업쪽에 큰 의미가 있습니다."

최양규 교수가 개발한 차세대 반도체 소자 기술 FinFET의 가장 큰 특징은 현재 반도체 소자로 사용되고 있는 실리콘에 나노 기술을 접목시켜 불가능으로 인식돼 왔던 3나노급 실리콘 소자를 개발할 수 있는 토대를 만들었다는 데 있다.

최 교수는 "반도체 소자의 소형화가 진행되면서 현재의 실리콘으로는 5나노 이하의 소자는 불가능할 것이라는 게 학계의 대부분 의견이었다"며 "때문에 반도체 소자를 갈륨 등으로 대체하는 새로운 재료에 대한 연구가 진행됐다"고 말했다.

현재 인텔에서 생산하고 있는 실리콘은 65나노급 정도. 2007년 45급 나노 반도체 칩을 생산한 뒤 2년 뒤에는 35나노급 칩 생산도 가능할 것으로 기대하고 있는 게 현실이다. 그러나 실리콘 소자로는 제 아무리 소형화시켜도 5나노급 이상은 불가능하다는 것이 일반적인 의견이었다. 반도체 소자의 소형화와 성능 향상이 한계에 다다랐다고 인정돼 온 셈. 하지만 이 같은 기우는 최 교수에 의해 소멸됐다.

최 교수는 "현재 소자로 사용되고 있는 실리콘으로 3 나노급 칩을 만들 수 있다는 데에서 실리콘을 이용한 칩 생산은 앞으로 20년간은 거뜬하게 됐다는 데 의미가 있다"고 말했다.

산업계에서는 획기적인 발견이었음에도 불구, 정부차원에서의 체계적인 지원은 없었다. 최 교수는 "FinFET은 엄청난 부가가치를 창출할 수 있는 반도체 소자 기술"이라며 "기존 연구가 진행되고 있는 기술에 대해서도 정부의 체계적인 지원이 필요하다"고 말했다.